我们使用支持快充协议的电源适配器给数码设备充电时,你可能并不会意识到,快充产品都经历了怎样漫长的进化之路。可能你是一位专业人士或发烧友,对快充协议的演进有一些了解,在经历几番混战之后,最终,快充市场的格局被定格——USB PD 一统天下,但是只要承认 USB PD 的“法定货币”地位、接受被收编的命运,其它快充协议依然可以活跃在自己的小王国里,收取授权费。

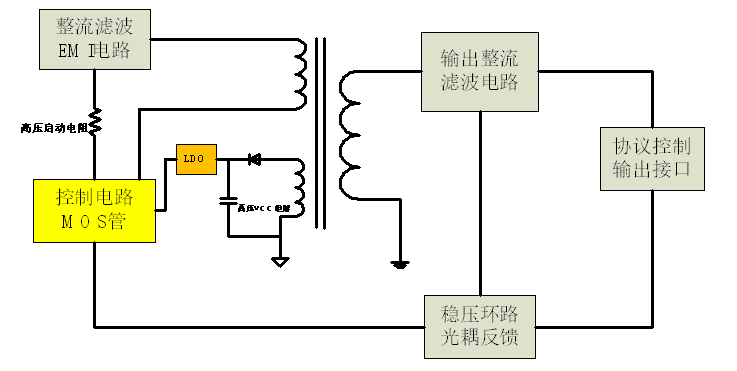

但今天,笔者要跟大家聊一聊快充产品另一项技术的演进——快充PWM控制技术。一直以来快充PWM控制器的一个关键点就是输出电压可调,且可调电压范围较宽(最终的PD协议要求范围为3-21V),而这些带来的最大问题就是PWM控制芯片VCC耐压不足。常见的措施例如普通PWM控制器VCC增加线性LDO降压,或者PWM芯片采用VCC高压工艺等。但这些措施本质上都是在做加法,增加线性LDO电路,增加了器件同时又增加了成本,电路也变得复杂,对待机功耗也产生了影响;芯片VCC采用高压工艺,增加了IC的成本,同时VCC的滤波电容耐压也会成倍提高,成本和器件体积会同时增加。

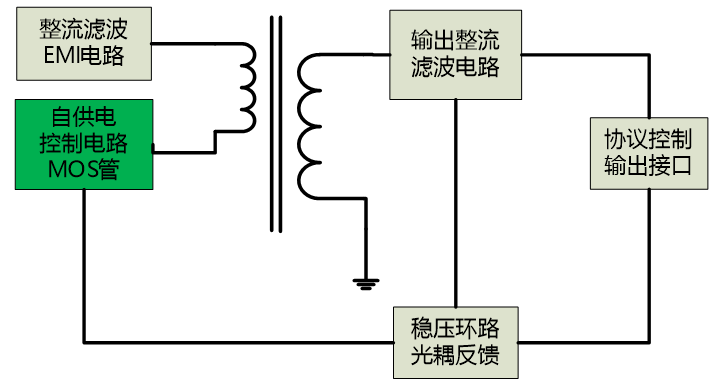

在当下这个电子产品供大于求的环境下,成本竞争已进入了白热化,特别是在适配器、充电器产品中,成本精细化程度可以说是分毫必究,小功率的适配器、充电器成本已成为了产品生存的关键因素。这时就需要技术创新来打破僵局,在很多人都做加法设计的时候,笔者也看到了一些不一样的产品,他们是在做减法设计,采用VCC自供电技术,省去VCC辅助绕组及其相关整流电路。

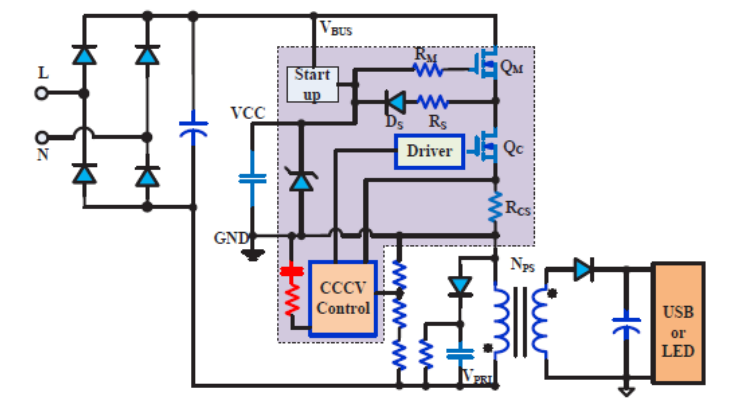

自供电技术早在多年以前,就已经出现在高校的博士论文中,最初是以原边反馈架构(PSR)为基础设计,采用源极驱动方式,通过控制内部源极驱动管来进行VCC充电。但因无VCC辅助绕组做反馈信号,只能采用浮地式设计,通过采样主绕组中的反射电压来控制电路进行恒压输出。这样的设计存在一个较大的系统劣势,采用浮地设计后,系统中电压动点变多,EMI效果明显较差,需要额外增加EMI滤波器件,另外原边反馈架构动态效果较差,而且在快充协议中,多需要副边反馈来进行电压申请,所以原边反馈架构的自供电方案并不合适做充电器及适配器类产品。

为适应市场需求,针对快充产品的特殊设计痛点,应运而生了副边反馈自供电双绕组方案。但自供电双绕组方案仍然存在一些技术难点,主要存在待机功耗较大的问题,难以满足欧盟的六级能效要求。

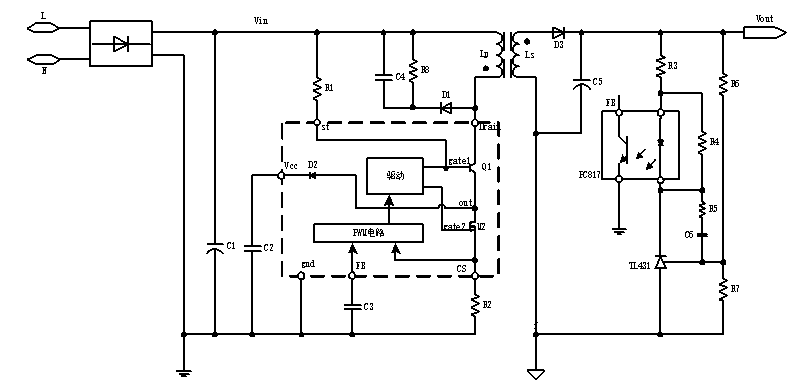

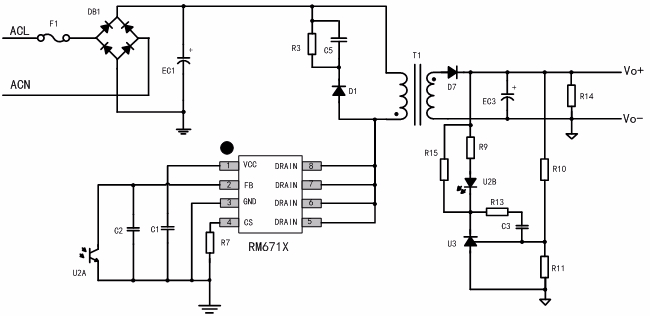

如上图自供电系统通过R1电阻给Q1功率管提供基极电流,经过Q1放大电流通过D2给Vcc外接电容C2供电,而C2提供整个开关电源控制芯片的工作电流,由于给C2供电时Q1管的基极电流只由R1提供,而为了考虑R1上损耗的问题,R1通常选取MΩ级别电阻,因此Q1在给C2供电时处在放大区,并没有饱和导通,所以Drain端电压接近高压输入电压,导致供电的损耗较大,难以做到六级能效标准。

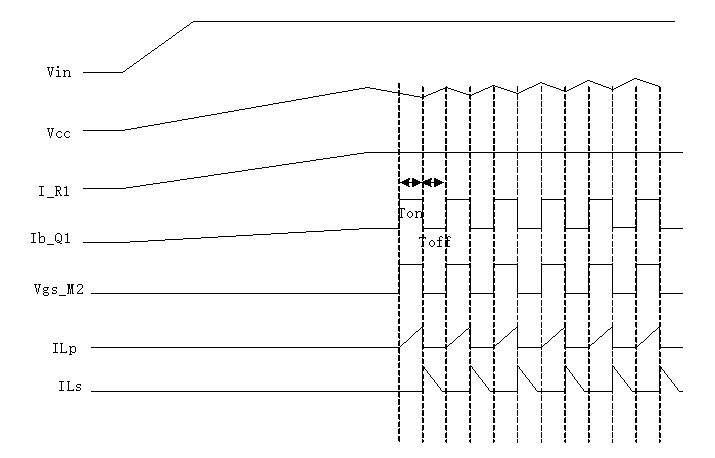

Vin:输入电压;I_R1:R1上的电流,为Q1提供一部分基极电流;Ib_Q1:Q1管的基极电流,在导通时基极电流主要由驱动提供,截止时R1给Q1提供较小的基极电流以使放大的Q1的IC电流给Vcc供电;Vgs_M2:源极驱动管的Vgs电压。

针对六级能效标准,需要采用特殊的VCC供电处理技术来满足待机功耗需求。在电源工作频率较高时可以通过自举供电保证VCC供电充足,但对于适配器或充电器等产品,存在空载工作模式,而空载时工作频率通常较低,且原边导通时间较短,因此单纯的自举供电方式无法满足芯片工作电流的需求。在原边导通时仍然采用自举供电方式给VCC电容供电,但由于频率低,一次自举供电的电量无法维持芯片整个周期的消耗的电量,则多个周期后VCC电容会持续放电至欠压保护,因此需要在轻载或空载时,一段时间内计时开启高压供电,以满足芯片耗电需求。通过采用自举供电和高压供电相结合,可在降低空载待机功耗的同时,满足VCC供电需求。

上述自供电技术已日趋完善,国内外众多芯片设计公司也在积极进行专利布局,业内也已有多家厂商推出了成熟产品,并已进入量产阶段。特别是一些国内IC设计厂商,已走在行业前列,相信很多业内人士对自供电双绕组方案也都有所耳闻,就在去年的2018(冬季)中国USB PD快充产业高峰论坛上,就有一家厂商对其自供电双绕组产品进行了宣讲介绍,有兴趣的朋友可以点击以下链接回顾了解。

此外,在上周刚刚结束的2019(秋季) USB PD&Type-C亚洲展上,该厂商对其多款成熟的自供电双绕方案进行了介绍,助推了这项技术的普及应用。随着这项技术的进一步完善,下游厂商将获得更为高效节能、安全可靠且成本更低的快充产品解决方案,快充市场格局或将为之改变。笔者相信未来会看到更多的自供电技术产品出现在快充展会上,这项技术能否带来行业技术革新,让我们拭目以待。

2018(冬季)中国USB PD快充产业高峰论坛PPT下载:亚成微电子

评论