自从小米推出33W氮化镓快充后,迷你快充的功率从20W提升到了33W。如何在20W的体积内升级到33W,成为了新的难题。

英诺赛科推出了一款全新的氮化镓器件INN650DA04,并通过多方位的优化,成功实现了超迷你的33W氮化镓快充设计。下面是英诺赛科33W极致小体积解决方案介绍。

英诺赛科33W极致小体积解决方案由邹艳波先生为大家讲解。

分享内容分为三部分,第一部分是针对30W到45W市场推出的英诺赛科INN650DA04特性介绍,第二部分是如何设计高功率密度的33W快充方案,第三部分是介绍基于InnoGaN的33W单C口和33W A+C口的解决方案。

首先来看英诺赛科INN650DA04的特性介绍。

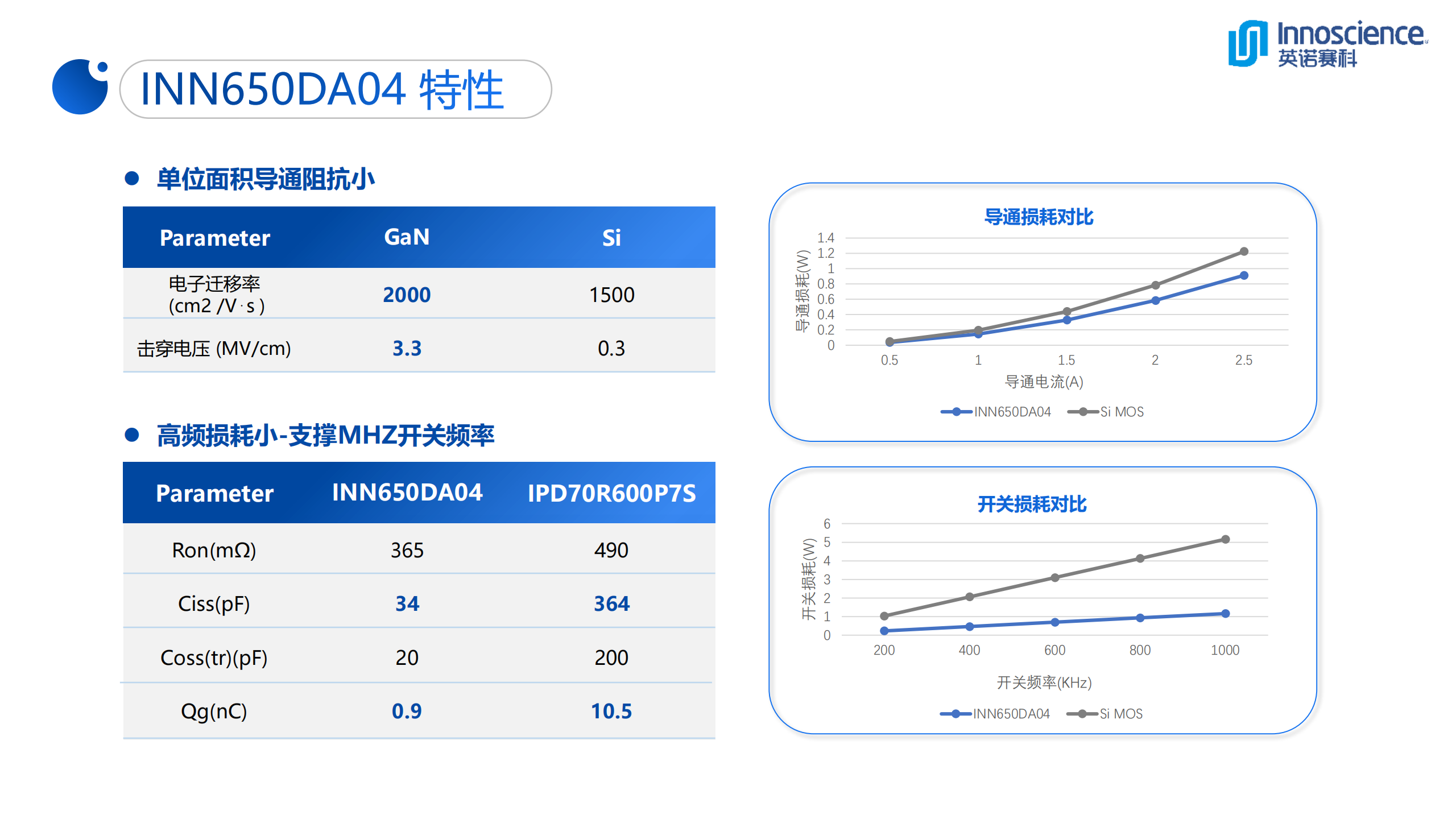

氮化镓具有卓越的材料特性,击穿电压远高于硅材料,是硅材料的10倍。同样耐压的器件,芯片尺寸可以做小,单位面积阻抗也可以做小,反馈到应用上,导通损耗就会更小。

另外显著的优势是Ciss和Qg只是硅MOS的1/10,降低开关和驱动损耗,开关频率可以达到MHz级,随着工作频率的提升,相比硅MOS的优势更明显。

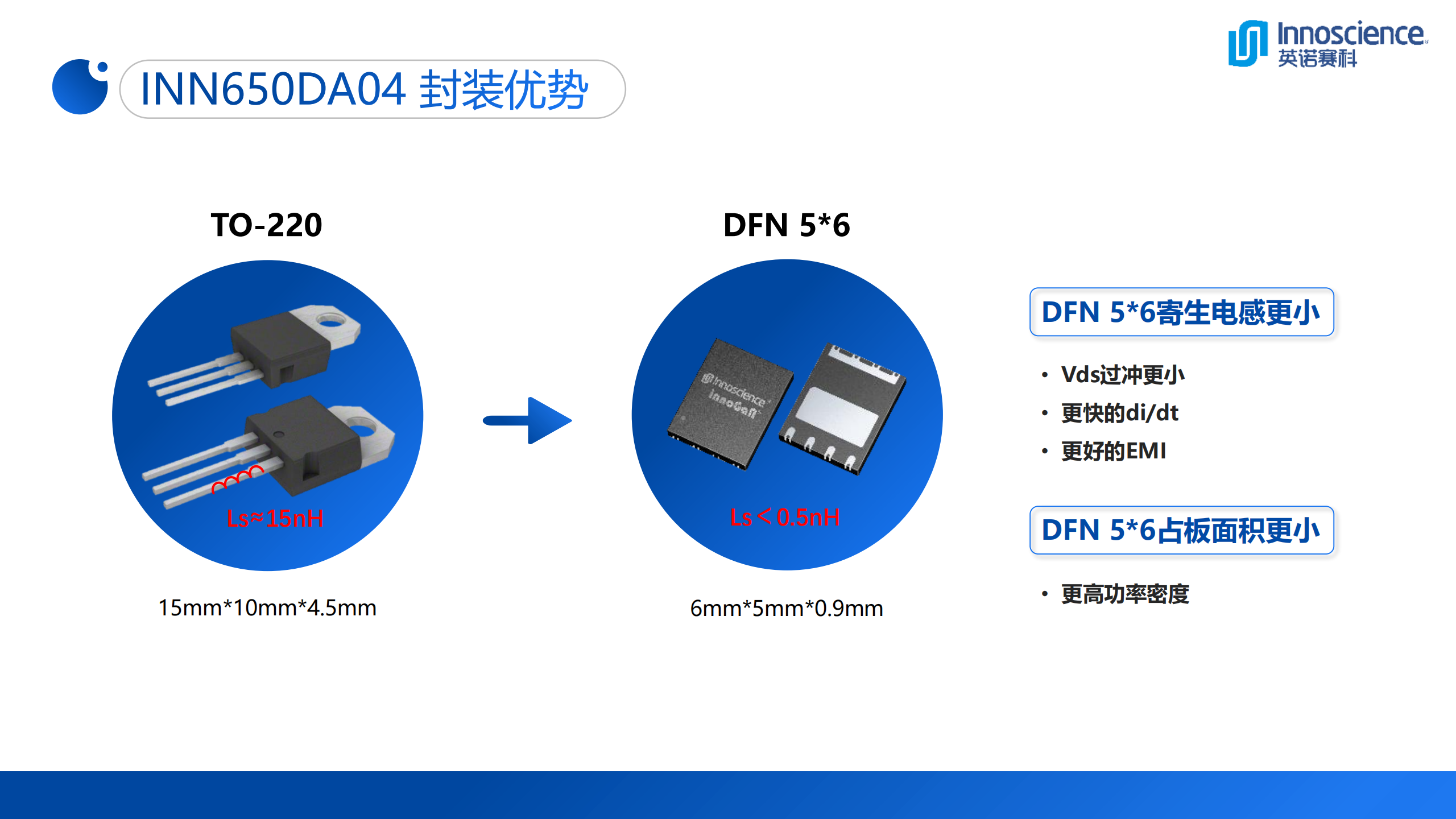

英诺赛科INN650DA04采用DFN5*6mm封装,相对传统TO220封装,寄生电感呈指数级减小,可以支持更快的开关速度和更高的工作频率,同时占板面积非常小。有利于高功率密度快充设计。

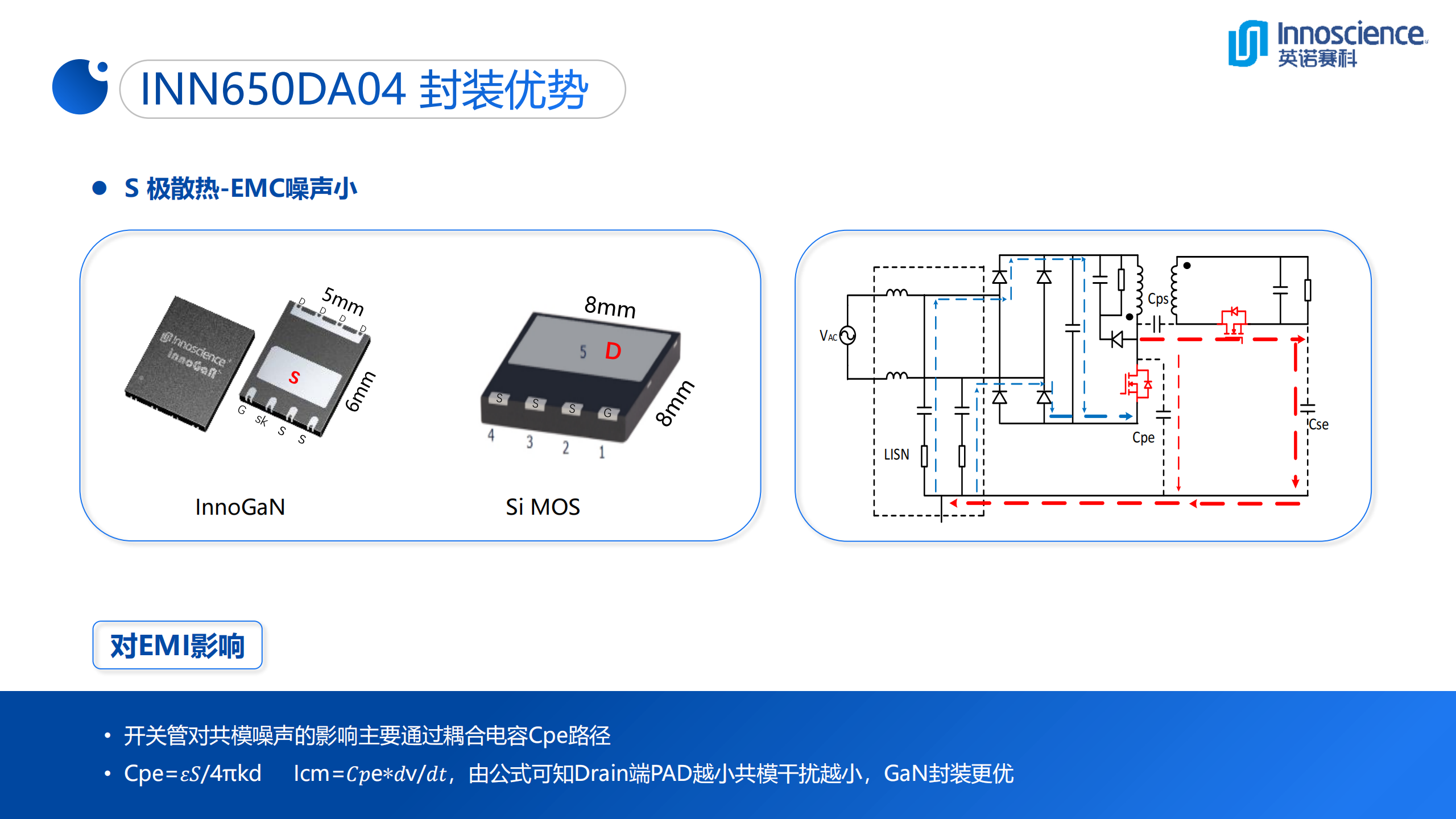

平面的氮化镓器件采用S极散热,相比传统硅MOS使用D极散热,具有EMC优势。硅MOS通过D极散热,面积较大,噪声辐射较大。INN650DA04采用S极散热,D极面积可以做到很小,噪声远小于硅MOS。

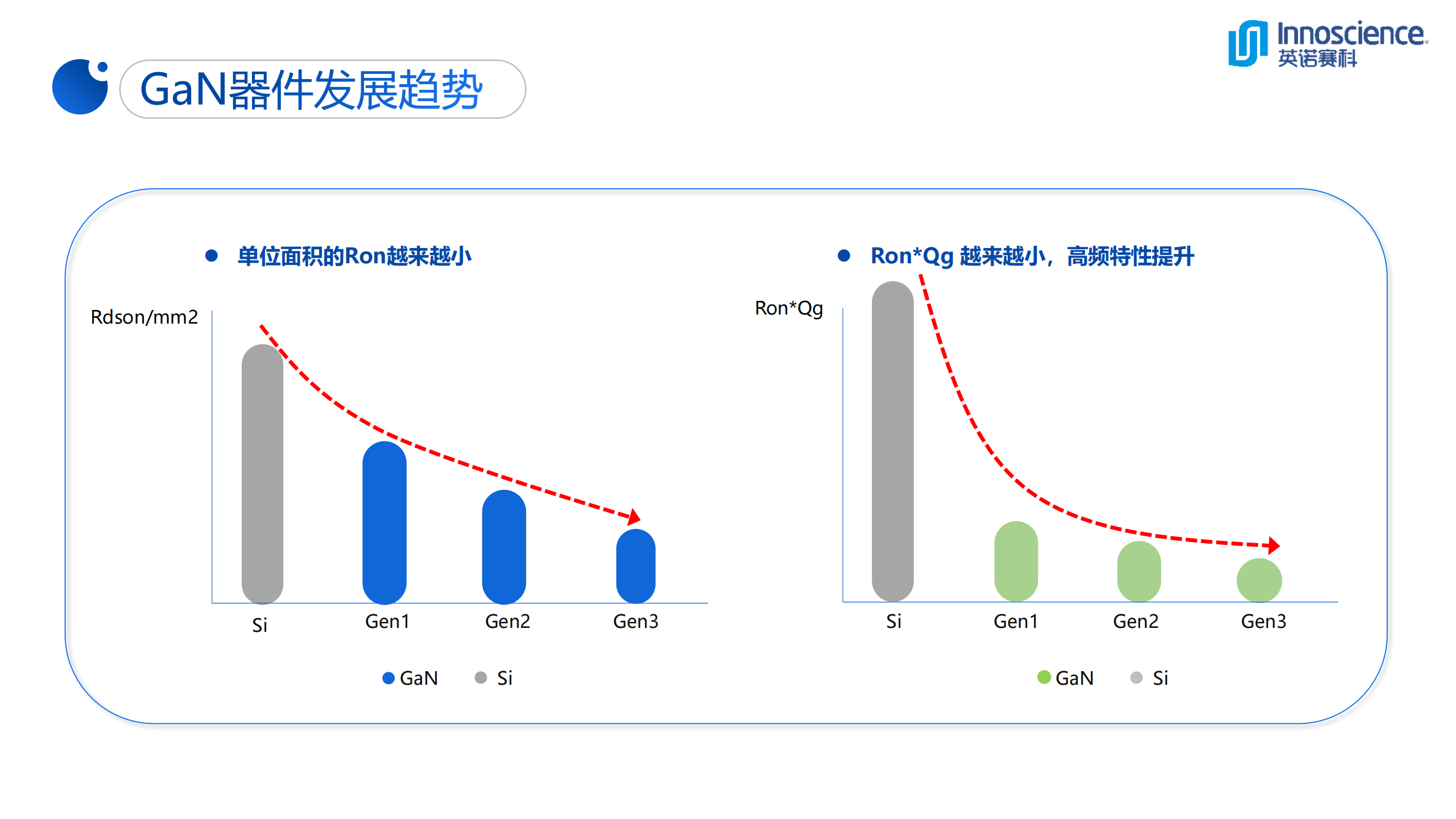

氮化镓材料具有很大的潜力,英诺赛科基于IDM模式优势,依靠自有晶圆厂,可快速迭代。随着产品迭代,氮化镓相比传统硅MOS的优势将会越来越大。

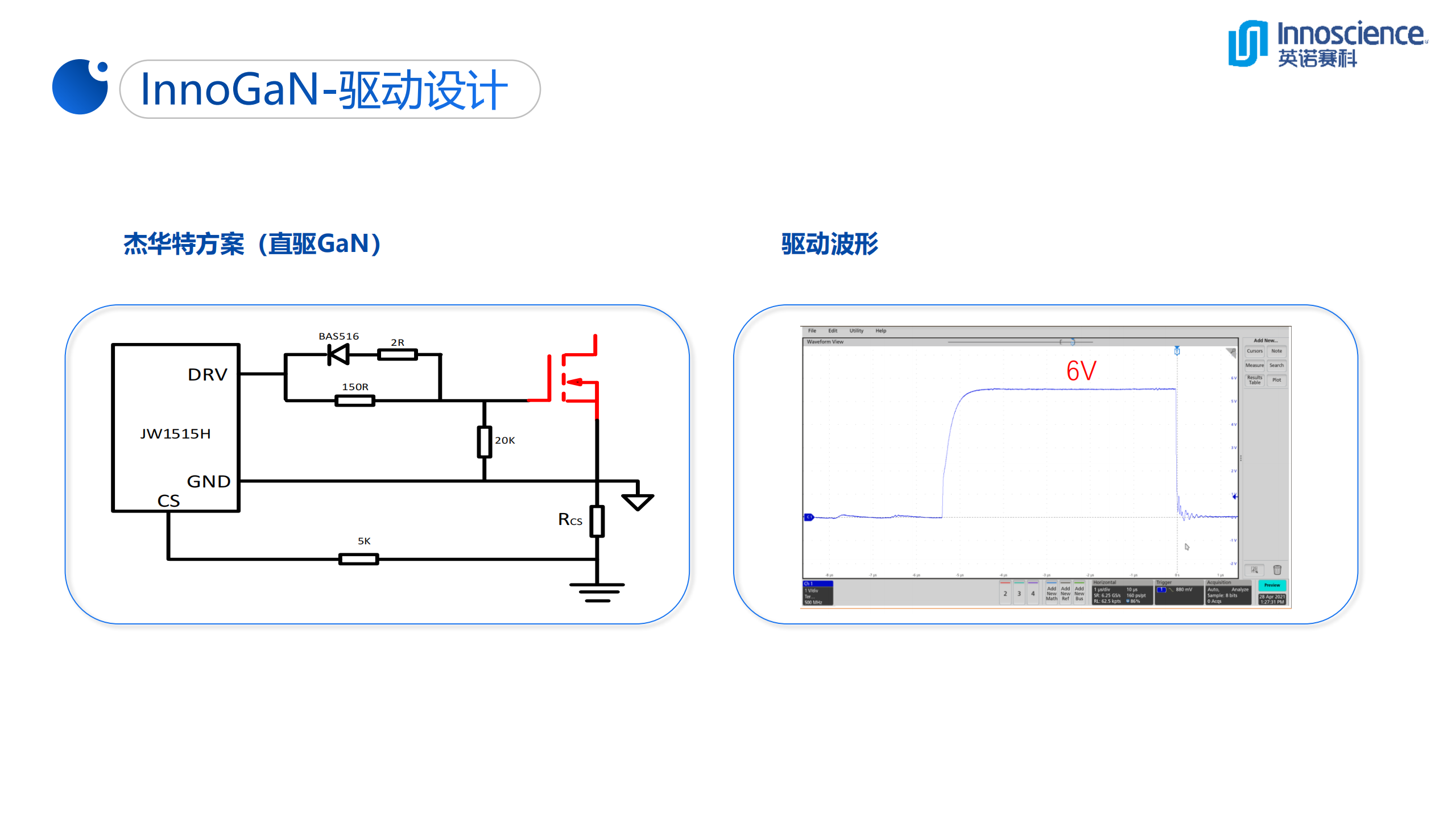

氮化镓驱动与硅MOS驱动设计不同,氮化镓需要5.5-6.5V驱动电压。业内IC厂家针对氮化镓推出了集成氮化镓驱动器的控制器。首先分享的是杰华特JW1515H控制器,其采用负压检测,驱动回路不受电流采样回路影响,为氮化镓器件提供稳定可靠的6V驱动,驱动波形非常平滑。

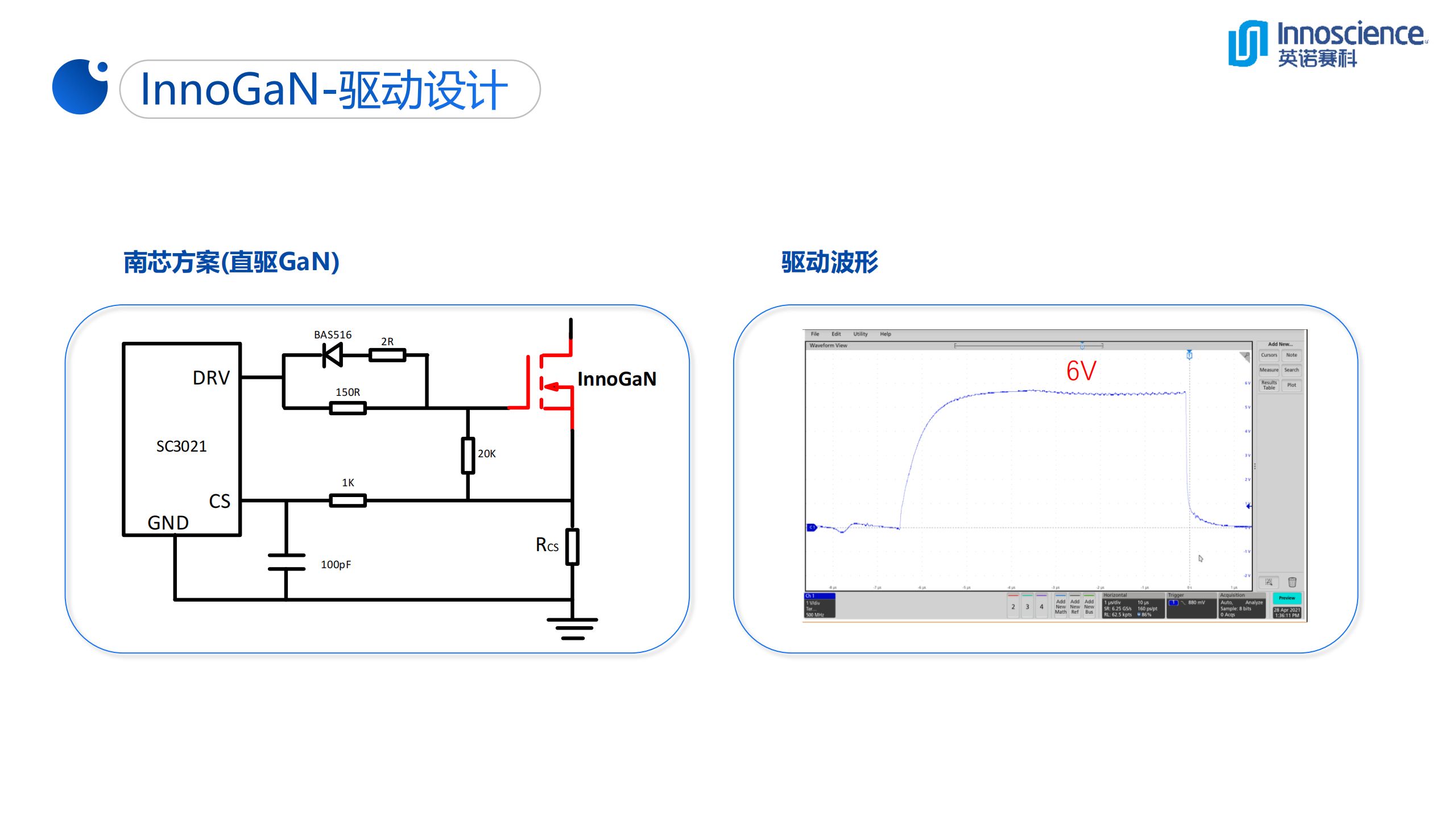

还有一个方案是南芯的SC3021,采用差分驱动方式,同样可为氮化镓器件提供稳定可靠的6V驱动。

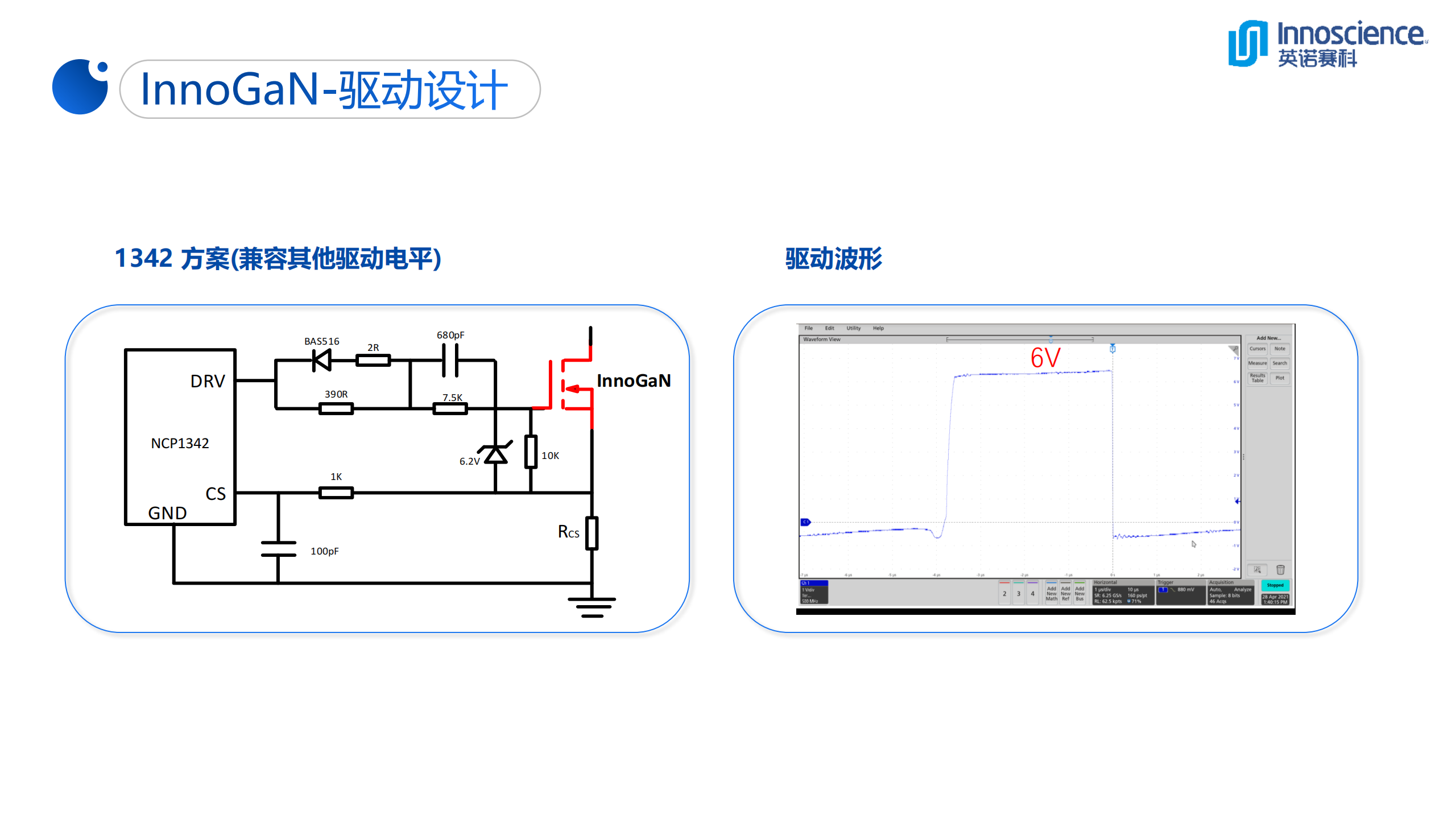

对于传统其他的控制器,可以通过增加RC电路和稳压管得到6V驱动电压为氮化镓器件提供驱动。

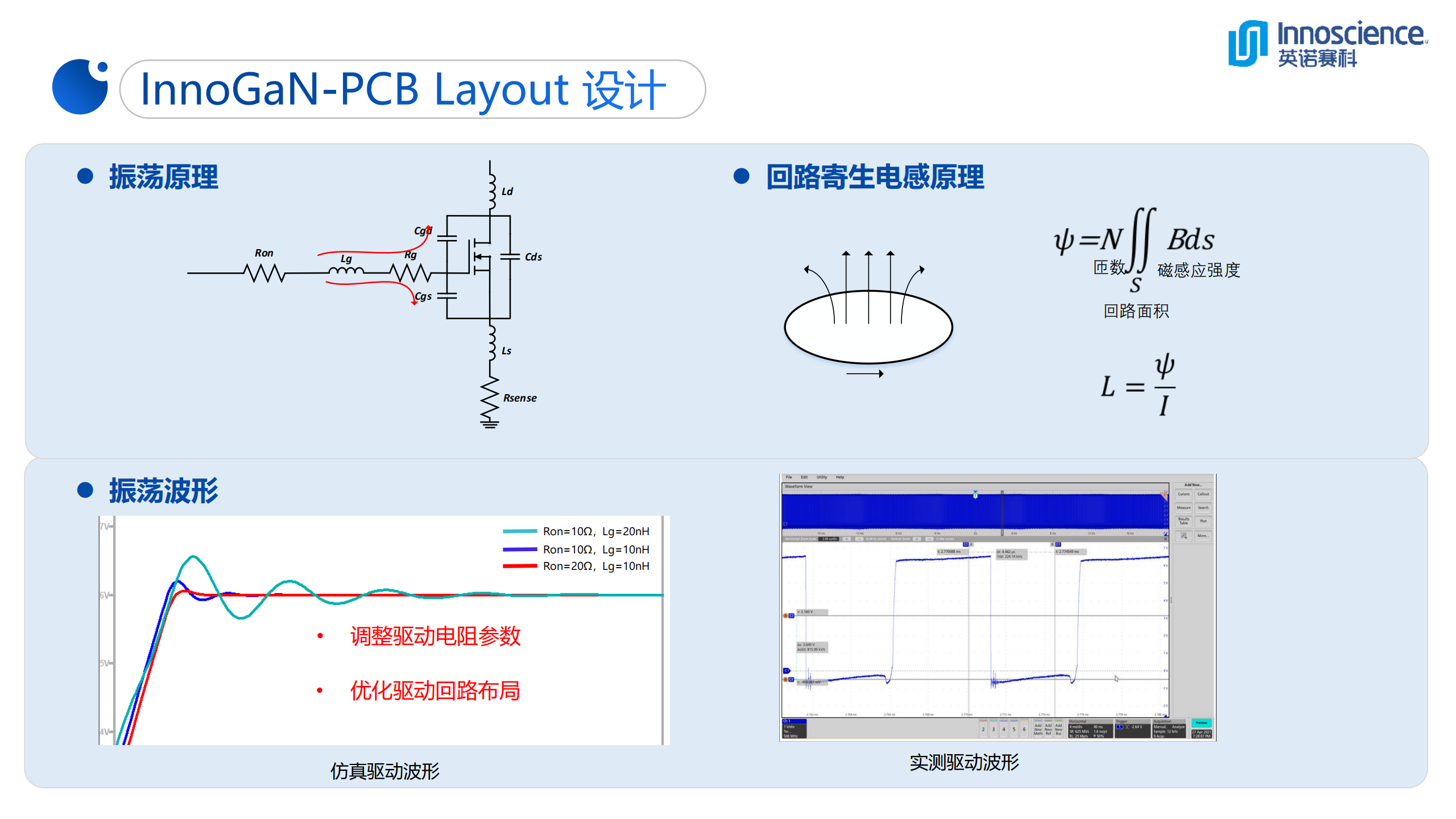

下面来看氮化镓驱动PCB Layout设计的注意点。理论上产生震荡是回路存在的寄生电感与寄生电容谐振。寄生电感和回路面积是正相关的,所以在Layout的过程中需要减小驱动环路的面积,以降低寄生电感,从而减小振荡幅度,并通过增加驱动阻尼,消除振荡,实测驱动波形没有振荡。

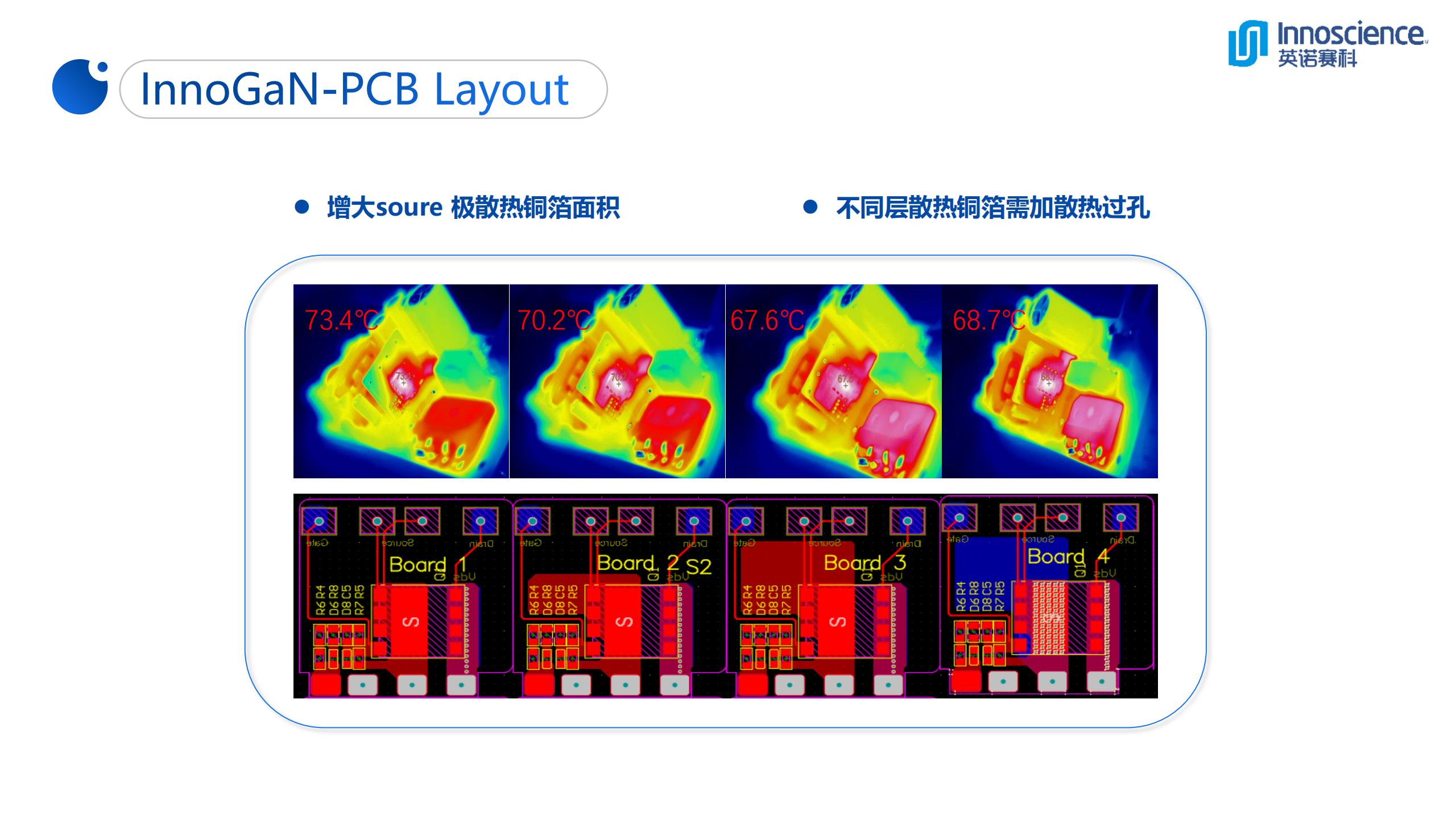

器件的散热可以通过PCB Layout的设计来优化散热,对比图1和图3,增大source散热铜箔面积,实现器件温度降低6度,对比图1和图4,通过增加source散热过孔加不同层铜箔,同样实现了温度5度的降低。

接下来是基于InnoGaN如何实现高功率密度33W设计。

在33W的小型化设计中,体积小,效率高和EMC都是比较重要的。在物理结构上要做小,需要综合评估小尺寸下的温升与效率的平衡。在高功率密度的设计,EMC器件体积受限,同时干扰也变得更加严重,EMC的处理非常关键。

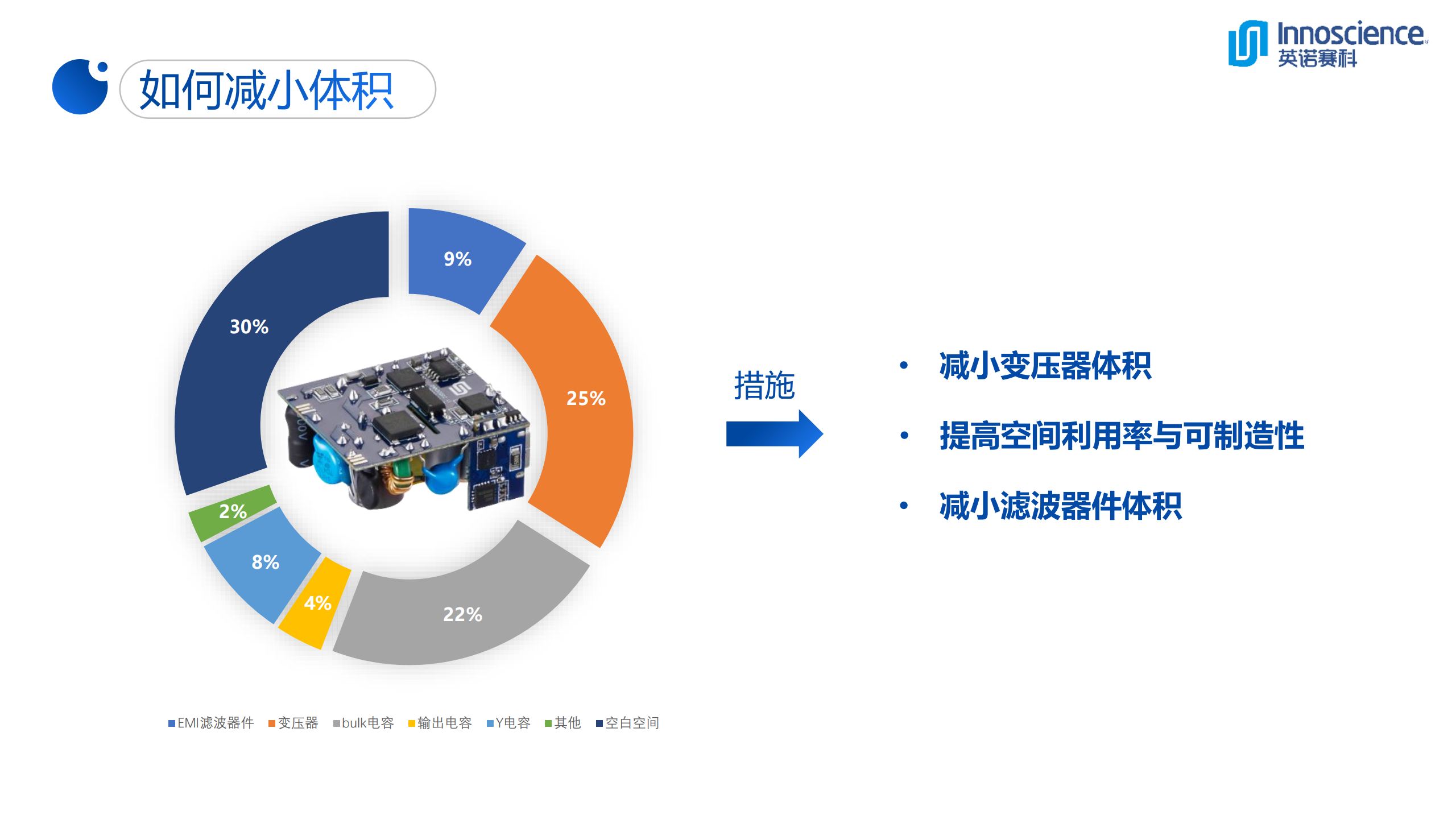

首先来看如何把产品尺寸做小。我们对快充模块各器件空间占比做了分解,主要占体积的是变压器、母线电容、滤波器件和未利用的空白空间。我们的思路是减小器件尺寸,同时充分利用未利用的空白空间,把体积进一步做小。

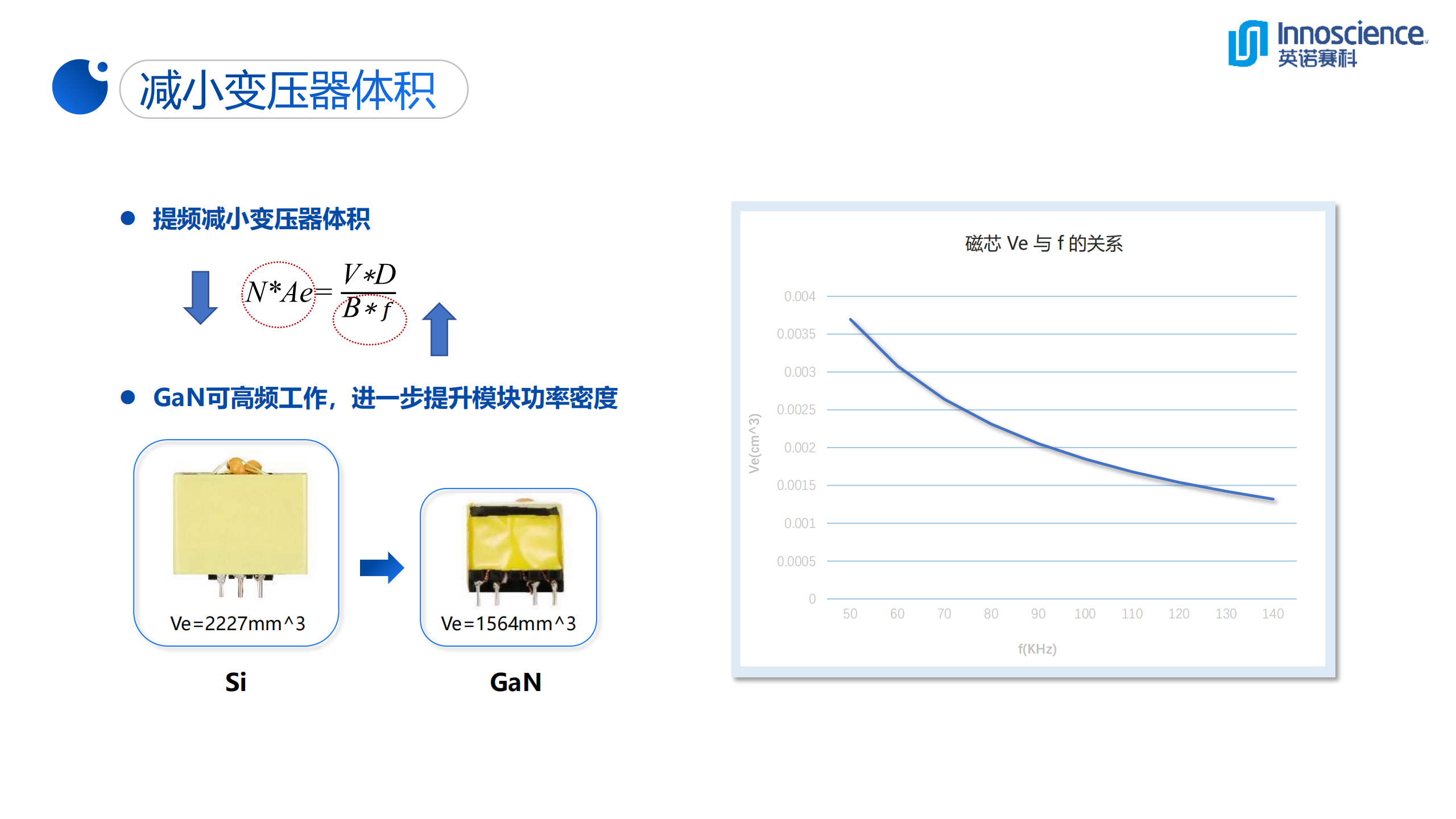

当前减小元器件体积的重点在于减小变压器尺寸。受制于磁芯材料的饱和特性,我们减小变压器体积的有效方式就是通过提高工作频率来实现。快充使用GaN之后,得益于GaN开关损耗非常小,性能和工作频率可以提高。在应用氮化镓方案的33W的设计中,相较硅MOS方案,在兼顾EMC处理的同时工作频率提高一倍,可以减小30%的变压器尺寸。

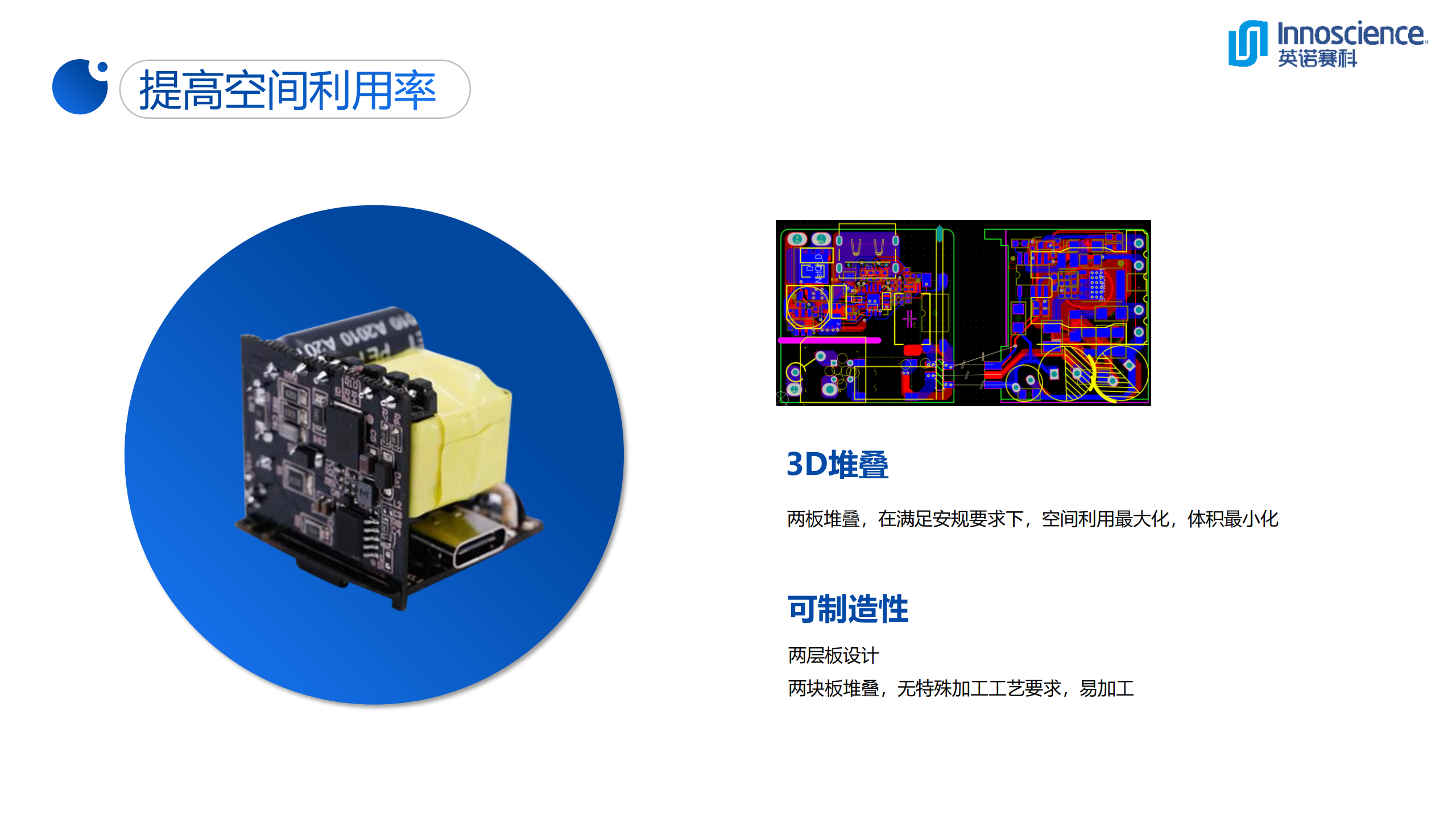

在空间利用率这块,我们可以通过3D堆叠的方式提高空间利用率,但要兼顾可制造性和加工成本。目前33W方案解决了传统方案采用3块板堆叠加工难的问题,采用两块板堆叠,大大减小加工难度。加工成本,和直通率都有保障。

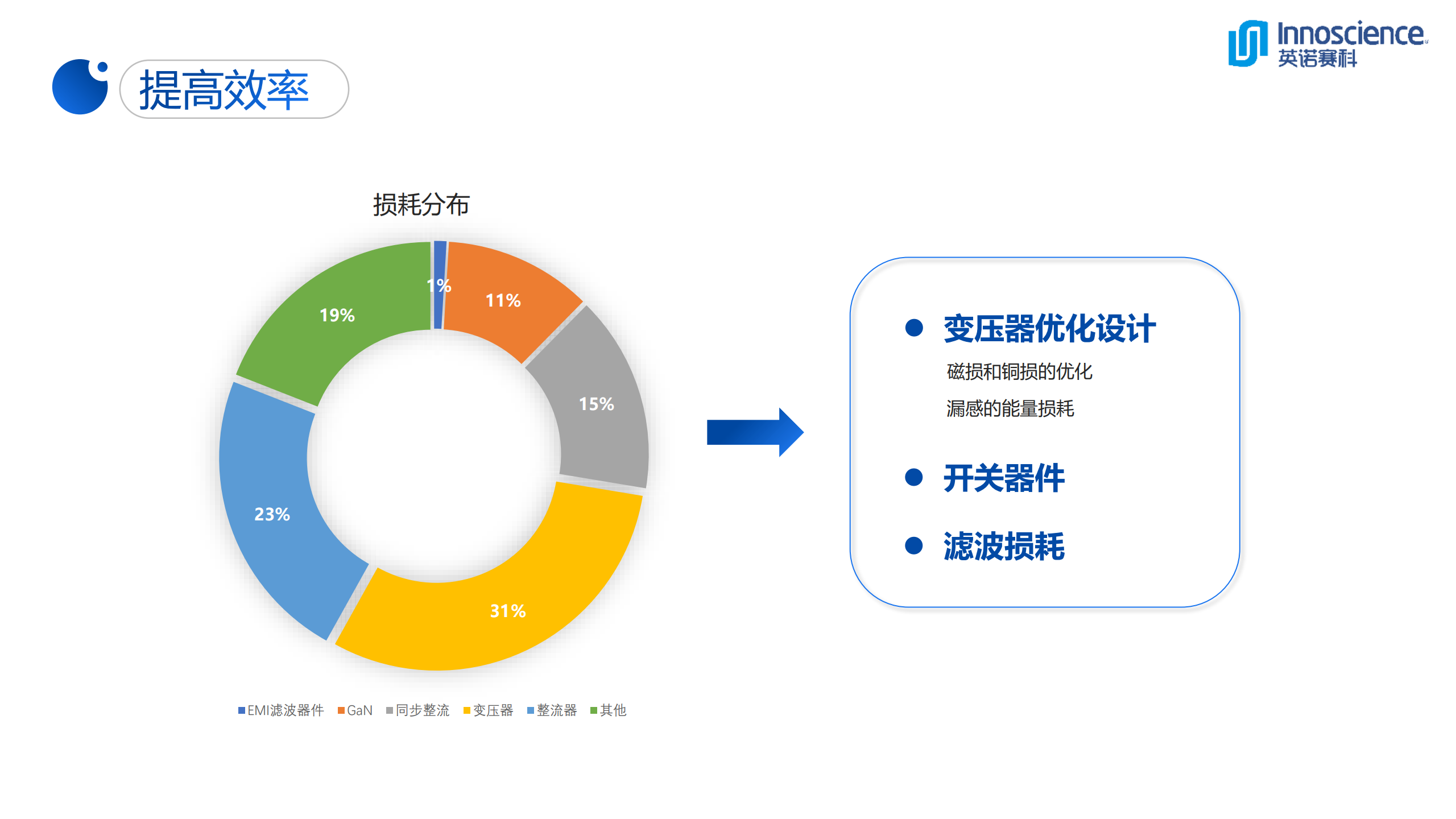

快充产品在结构上实现小型化还要考虑小尺寸下散热能力,根据散热能力去反推效率。根据快充损耗分解的饼图,损耗集中在整流桥和变压器上,还有开关器件。整流桥上的损耗,在大功率产品可以使用无桥PFC。小功率产品考虑成本和尺寸受限,重点从开关器件和变压器着手降低损耗。

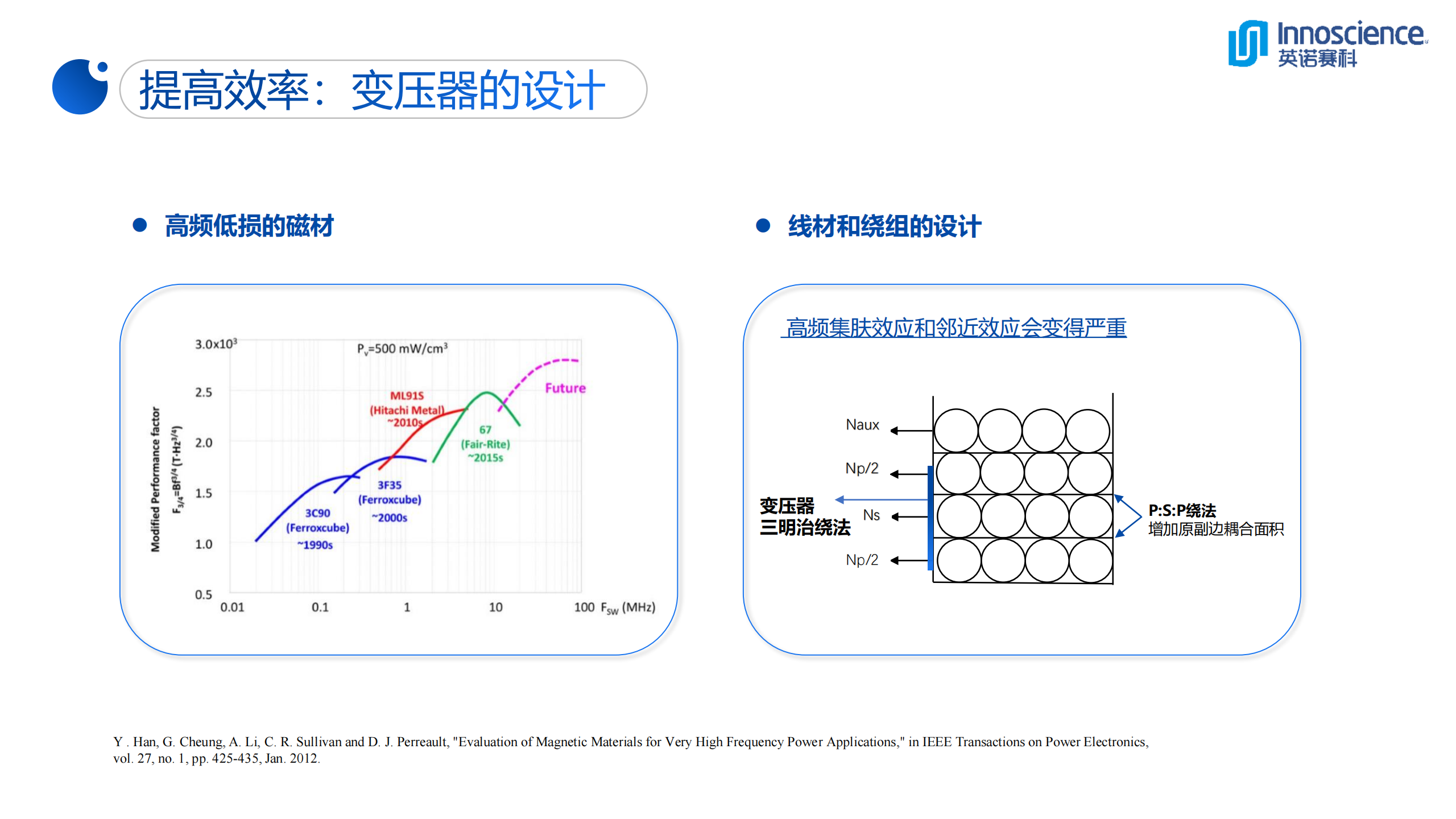

变压器的效率提升分为两块,磁芯材料和线材与绕制方式。根据工作频率和、工作温度及应用场景选择合适的磁芯材料。线材和绕组的设计,在高频时要考虑趋肤效应和邻近效应,降低损耗。

同时绕组结构的设计也非常关键,反激拓扑中变压器的漏感损耗对效率影响明显,需要减少变压器的漏感。通过绕组采用三明治绕法,配合密绕,增加原副边磁通耦合,副边出线尽可能短的方式可以有效减小漏感。

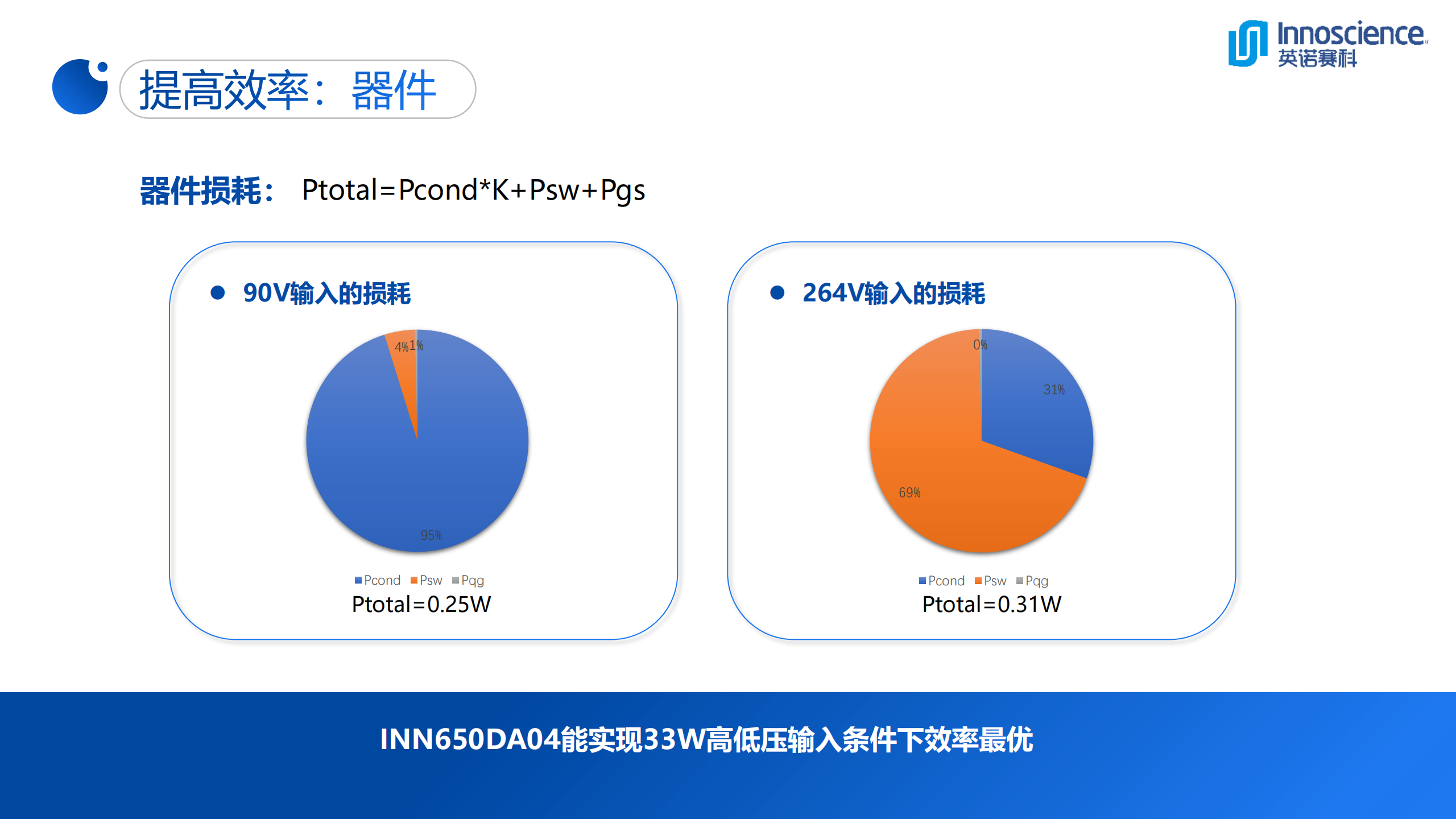

开关器件选型也非常重要。开关器件的损耗分为导通损耗,开关损耗和驱动损耗。我们不能盲目认为导通电阻越小越好,需要同时兼顾90V输入和264V输入的场景下的器件总损耗。90V输入下,QR为零电压开通,开关损耗较小,但电流较大,左边的饼图上可以看到导通损耗较大。在264V输入下,电流相对较小,器件处于硬开关,开关损耗较大,损耗集中在开关损耗。33W的设计采用INN650DA04可以很好的实现90到264V输入下效率的平衡。

接下来来看EMC问题的处理,EMC主要包括RE和CE。其中CE分为共模噪声和差模噪声。

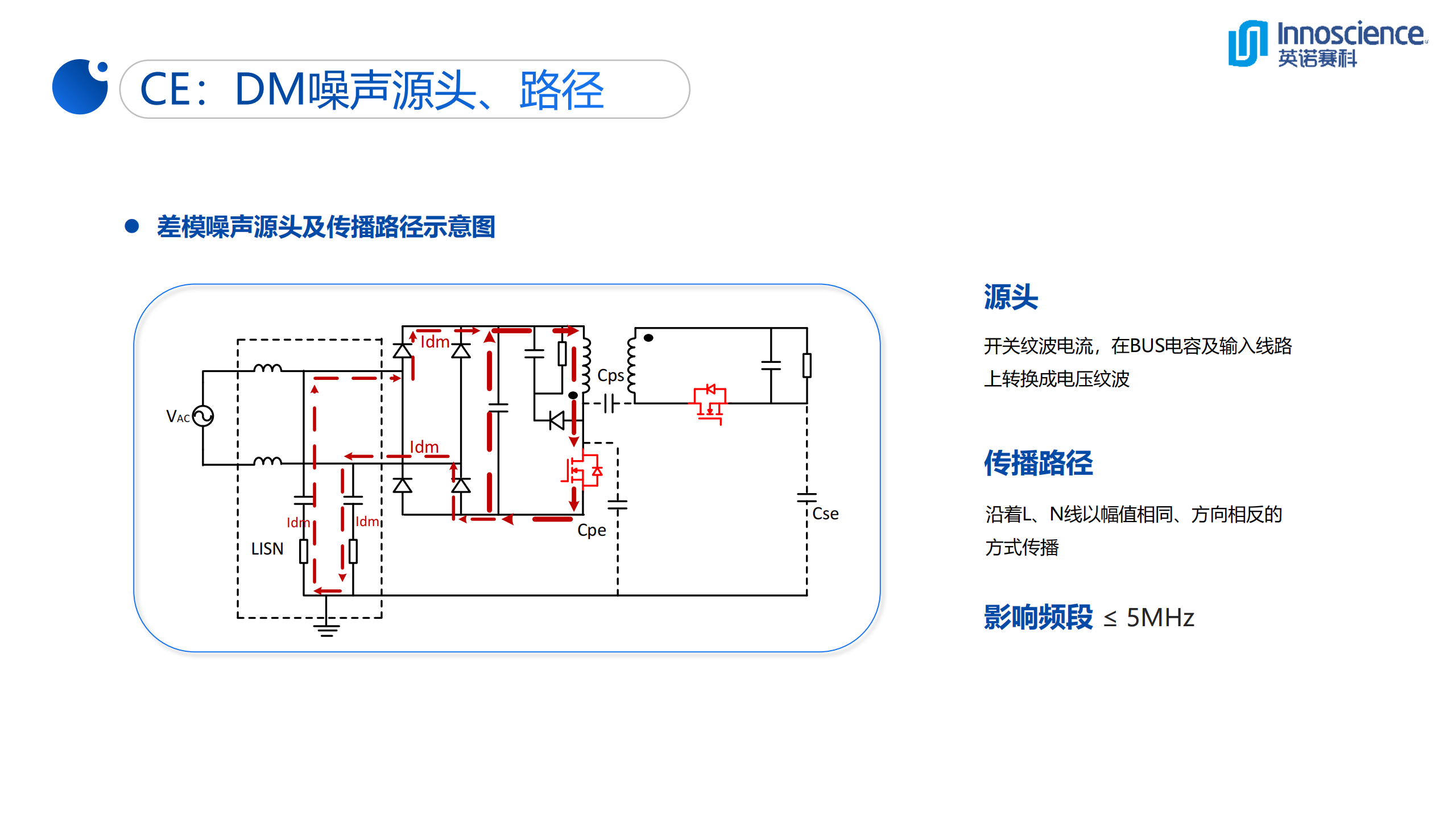

首先来看差模(DM:differencial mode)噪声。上面示意图给出了噪声源头和路径。源头是变压器原边开关电流纹波在BUS电容上产生的电压纹波噪声,并通过L、N线向外传递。主要的影响频段是5MHz以下。

BUS电容(铝电解电容)ESR越低,其两端的电压纹波噪声越小。

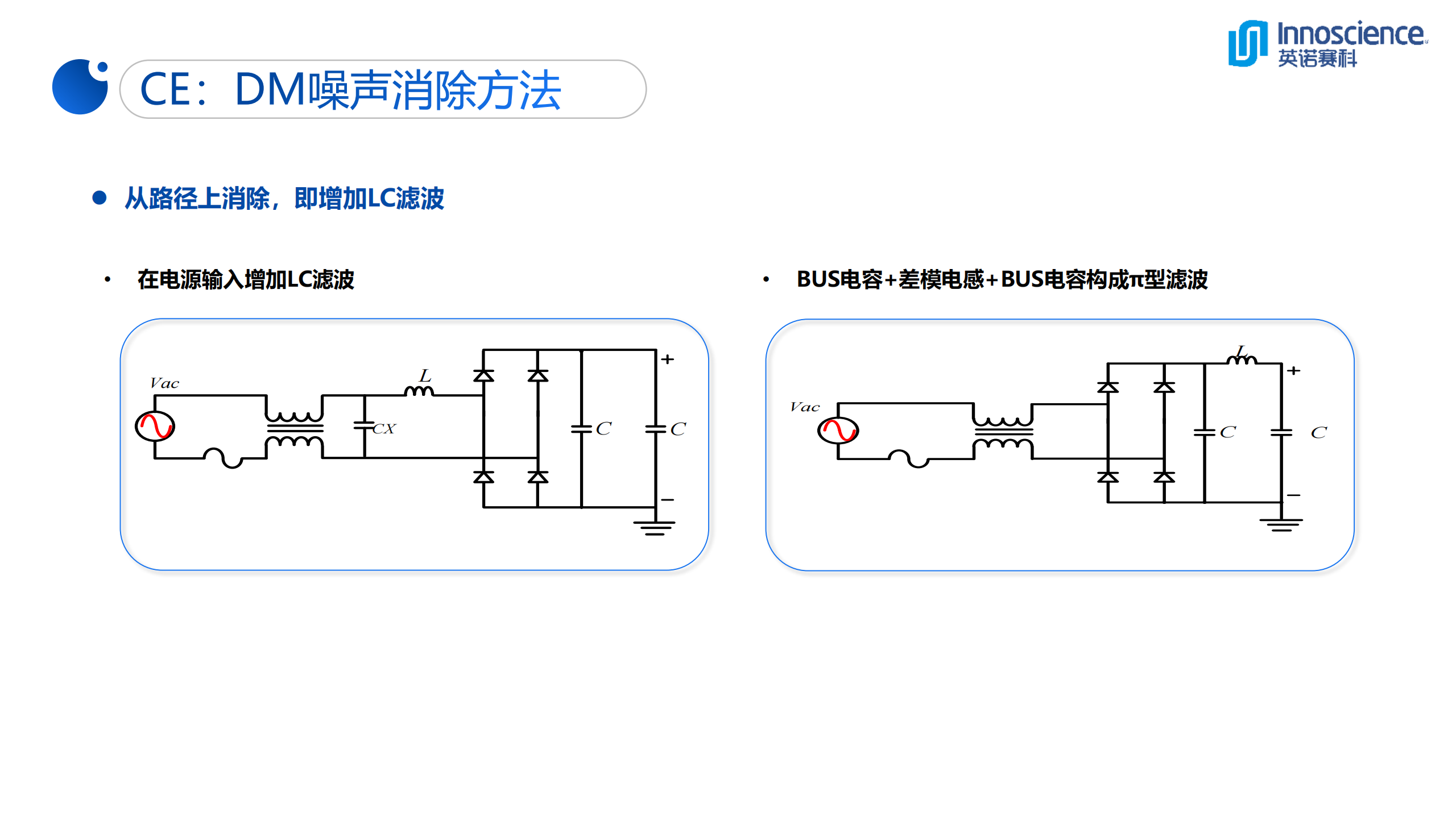

针对DM噪声的处理,我们主要是从传播路径入手,采用LC滤波,对噪声进行衰减。滤波方法包括:整流桥前加LC滤波,和整流桥后面的Π型滤波。

33W氮化镓方案采用Π型滤波。采用Π型滤波可以省去X电容,且可以使用低成本的工字电感,占板面积小。但需要注意测试工字电感前BUS电容的浪涌电压压力(BUS前电容承受大部分浪涌电压),及电感后电容满载时的温升问题(电感后电容承受大部分开关纹波电流)。

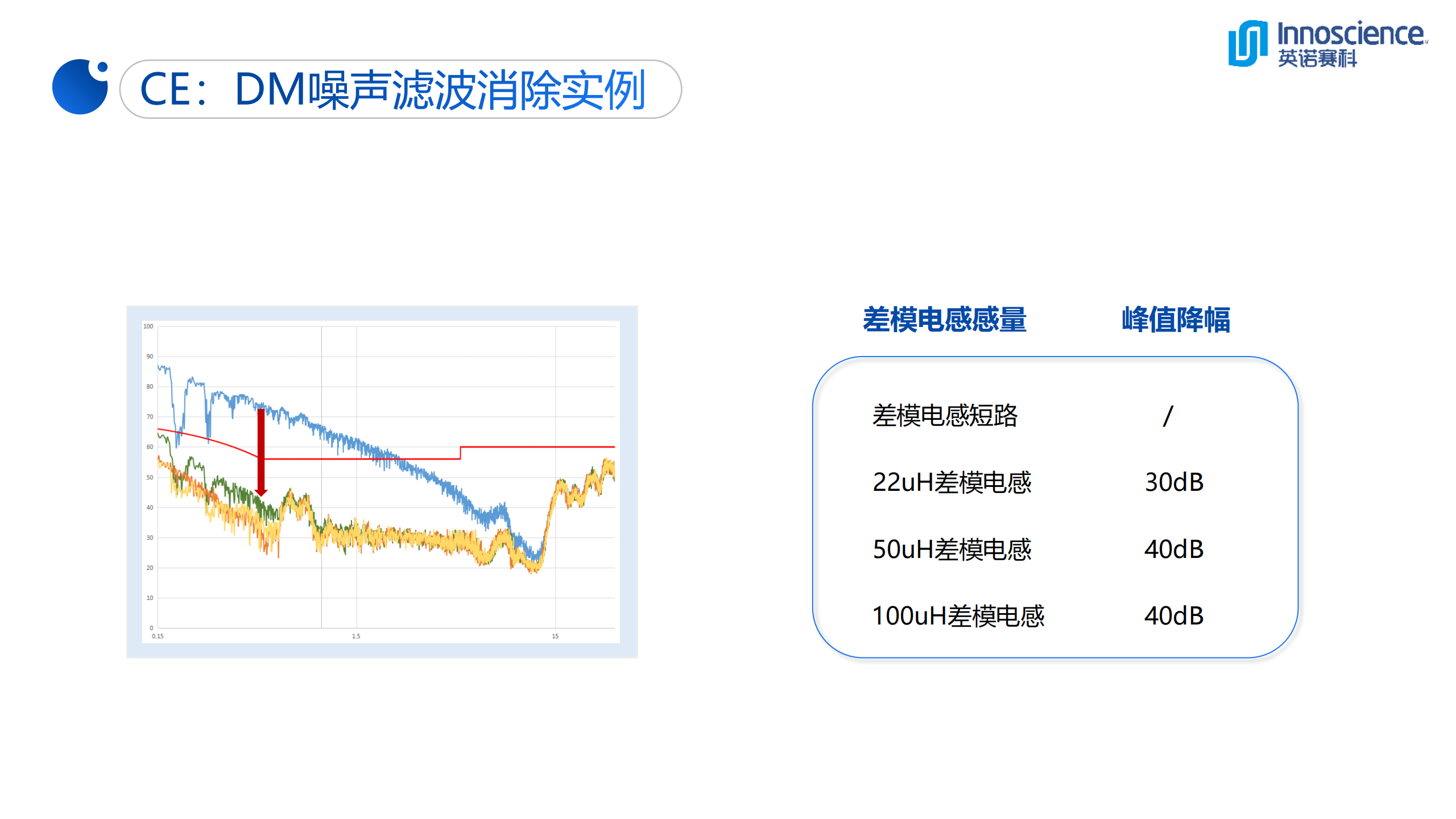

上面不同感量差模的噪声曲线,50μH效果较好,差模电感感量再增加,噪声裕量收益不明显。

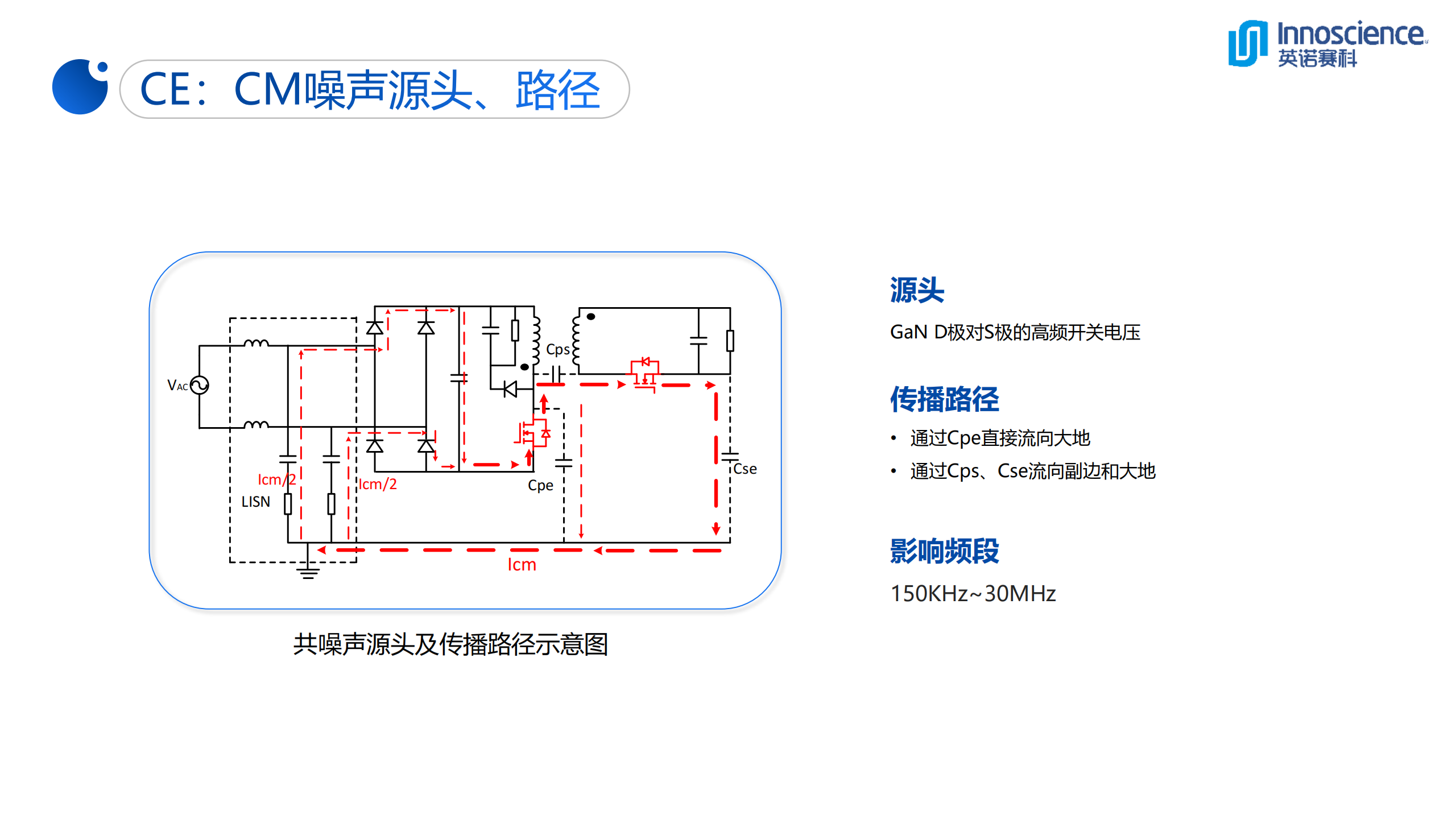

接下来是共模(CM,common mode)噪声,上面示意图可以得出共模噪声的源头和路径。共模噪声源头是由GaN高速开关的电压波形。该噪声一方面通过GaN管D对大地的电容(Cpe)直接流入大地,同时也通过变压器原副边电容(Cps)及副边与大地电容(Cse)流入大地;再经过LISN及L、N线回到GaN S极。其中,由于Cpe容量远小于Cps及Cse,故变压器原副边电容(Cps)及副边对地的电容(Cse)构成的路径是共模噪声的主要路径。

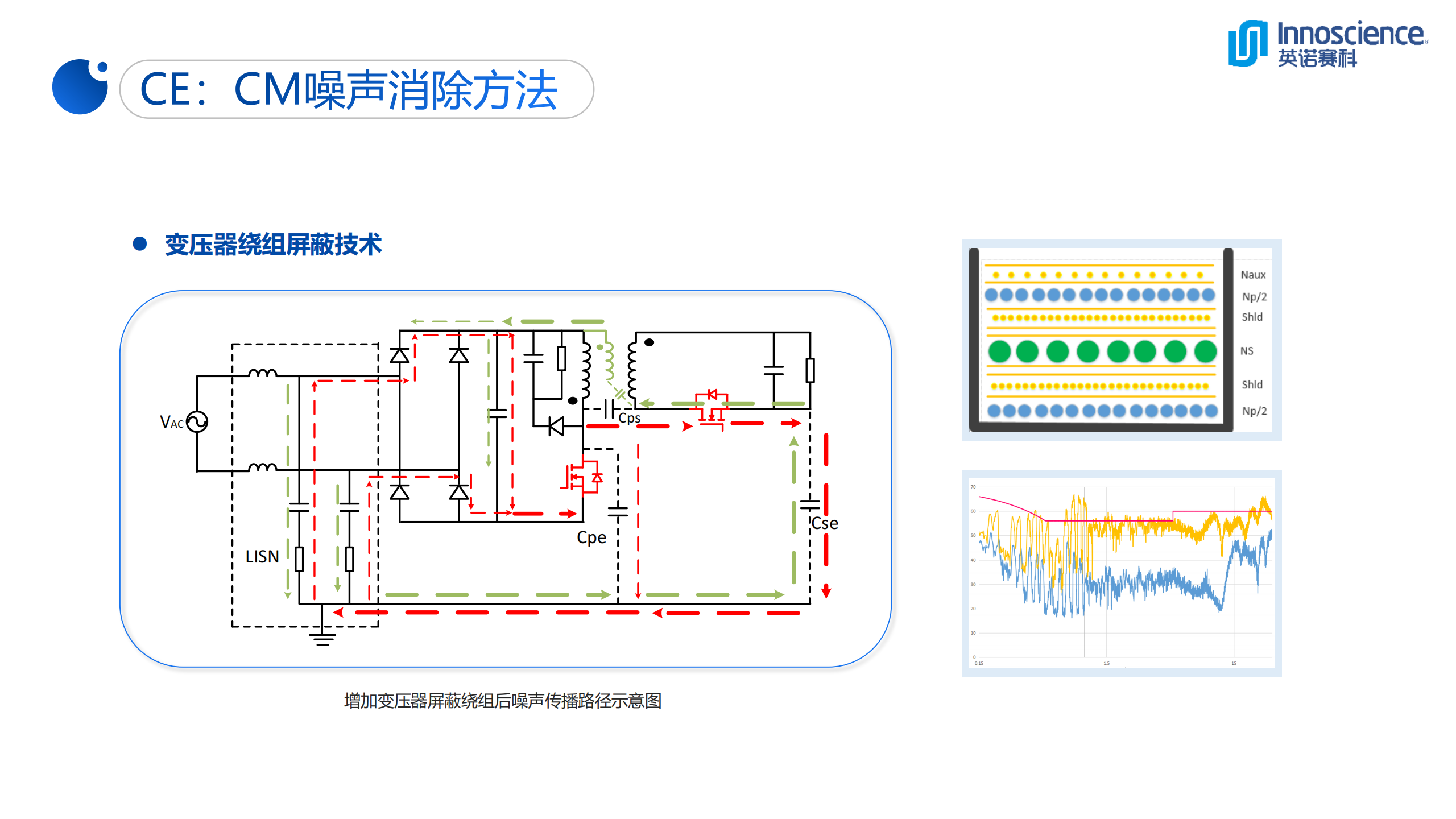

减小共模噪声,可通过优化变压器设计实现,上面右侧示意图中蓝色部分是在变压器绕组内的屏蔽抵消绕组,该绕组产生与源噪声相抵消的噪声,达到减小共模噪声的目的。

增加屏蔽绕组后可实现10-20dB的噪声衰减。

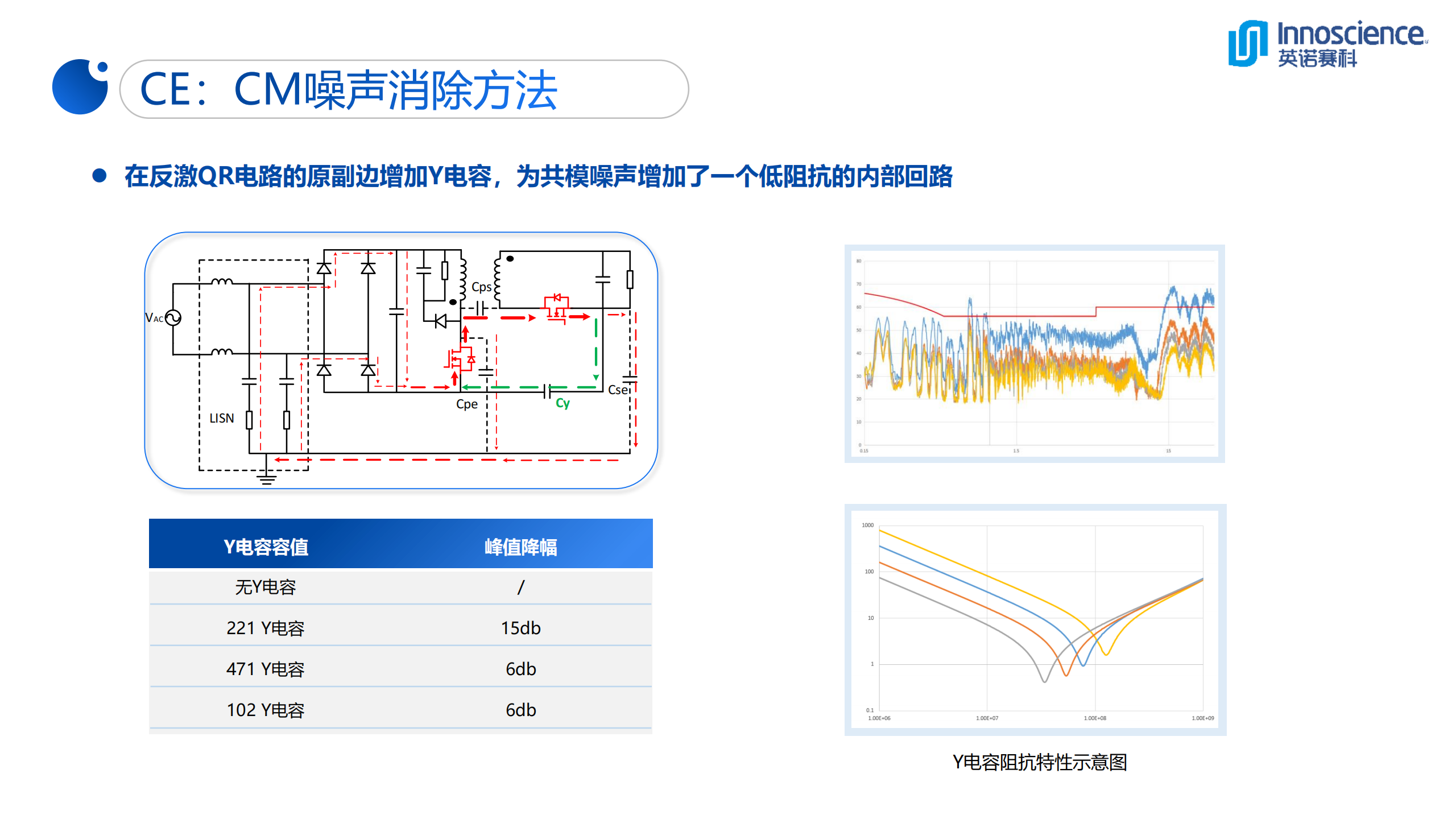

增加Y电容也是减小共模噪声的重要措施。Y电容构成了共模噪声的低阻抗回流路径,减少共模噪声进入大地和LISN的。

对于CE频段的共模噪声(0.15~30MHz),Y电容容量越大,传递出去的共模噪声越小;但Y电容选择需要兼顾最大允许漏电流的问题(Y电容容量过大,快充电源漏电流超标)。

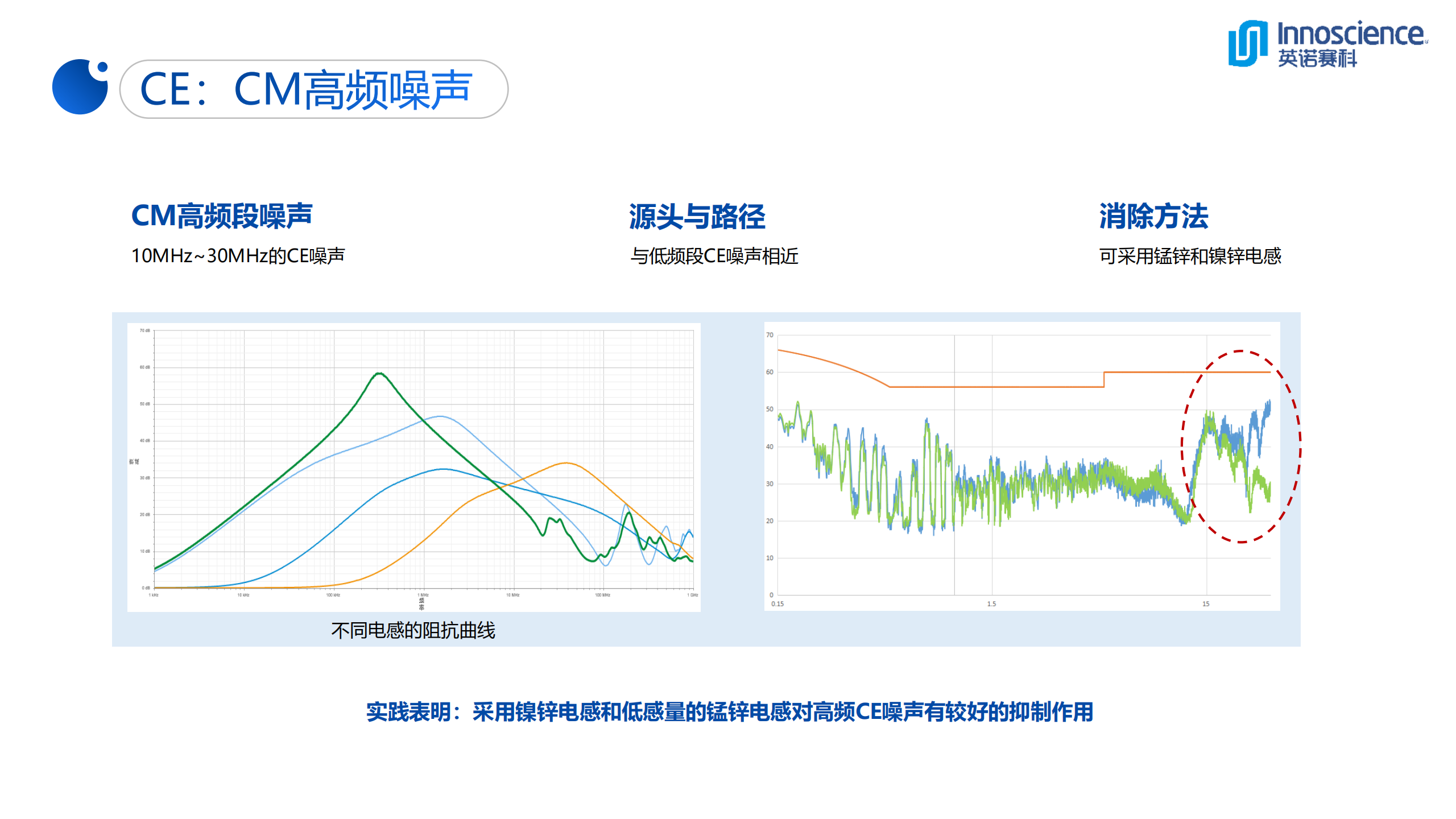

对于高频段(10-30MHz)的共模噪声抑制,在输入口增加镍锌电感是很好的选择。

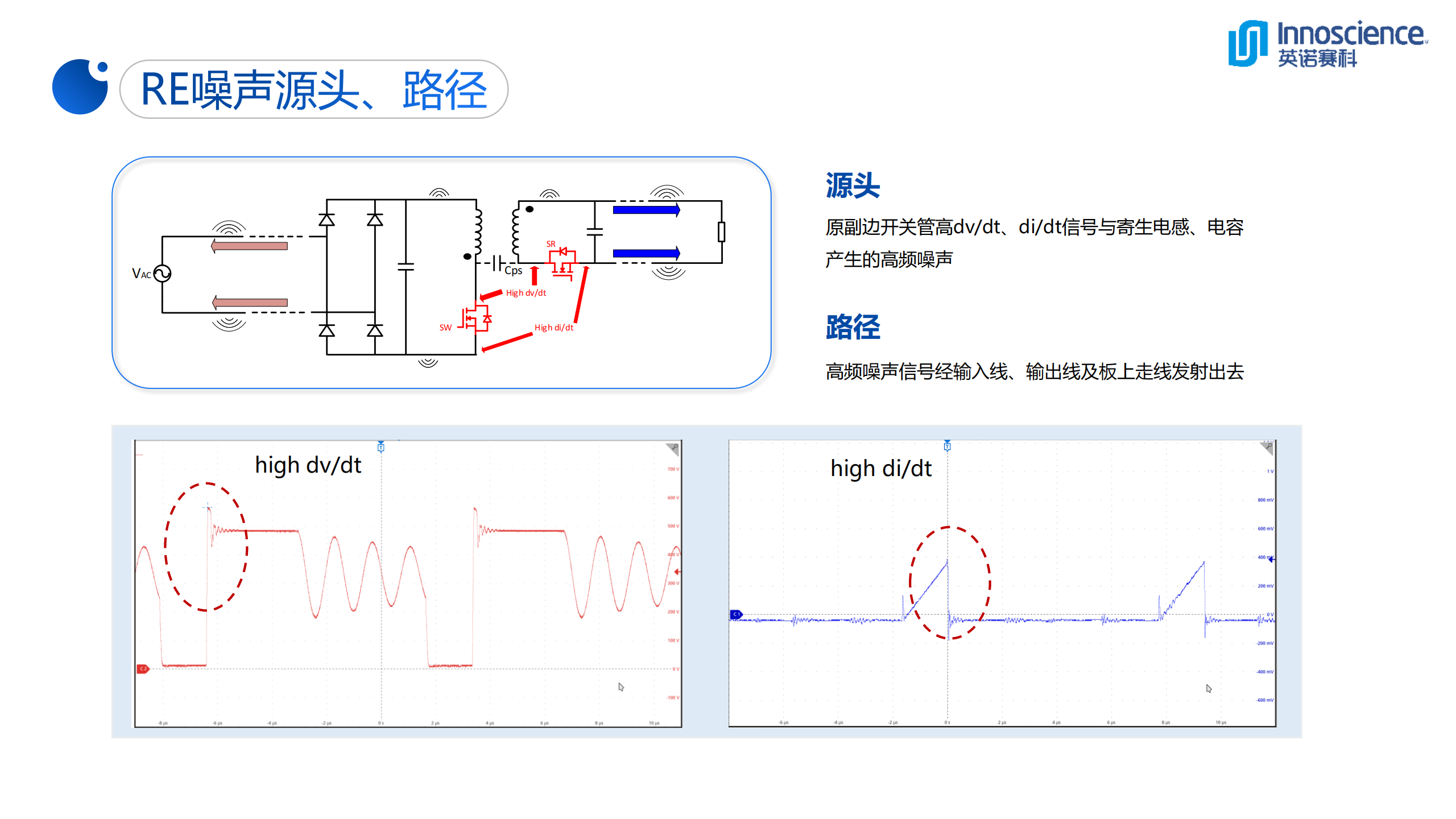

RE噪声是电源高频开关下,高dv/dt、di/dt特性的开关波形在寄生电感、电容上产生高频噪声,通过电源板上铜箔、走线及输入、输出线路形成的天线对外发射。

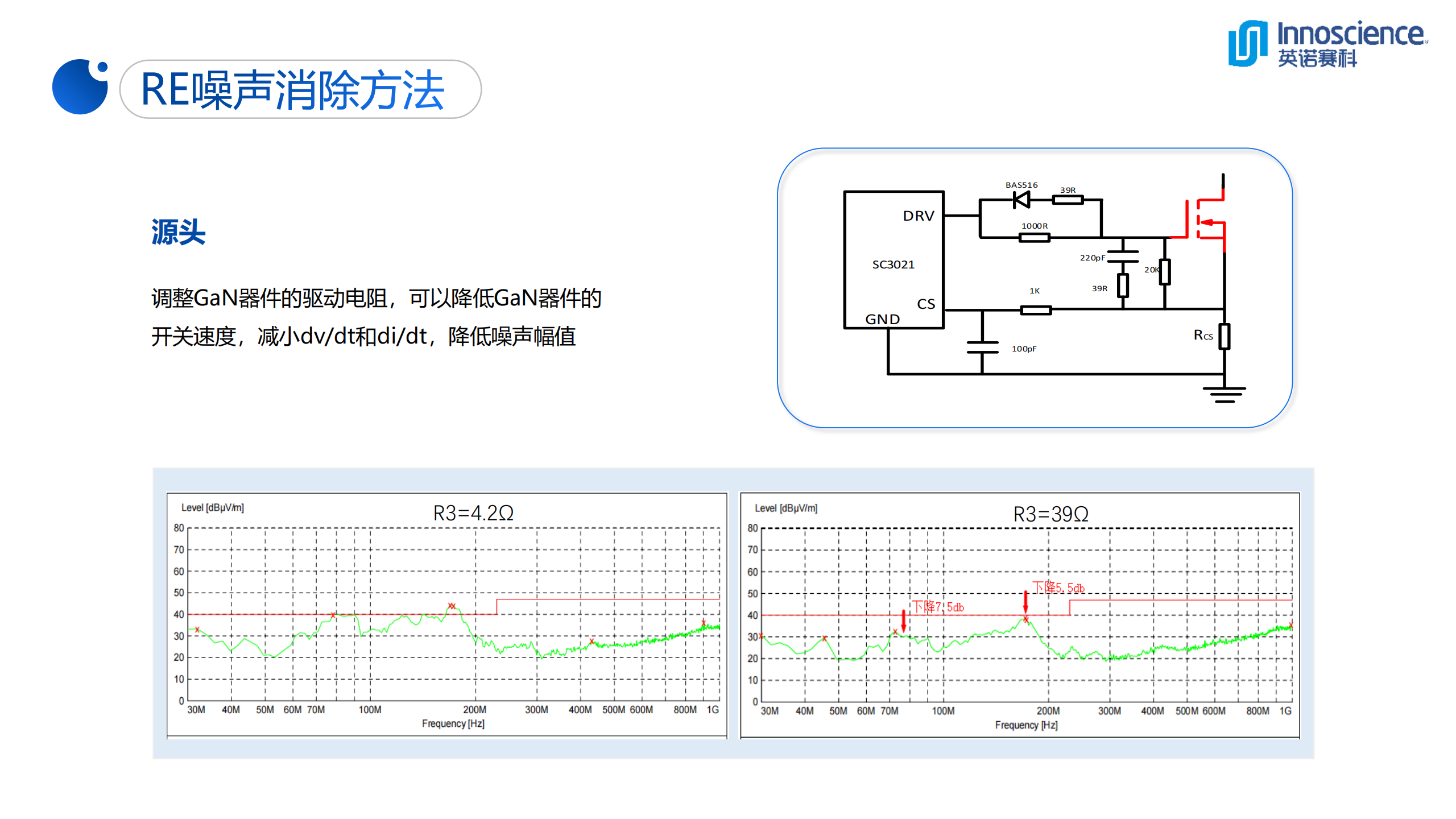

调整驱动电路的参数,降低开关波形的dv/dt、di/dt,可以从源头上减小噪声。该方法灵活、实用,这也是分立GaN器件的显著优点。

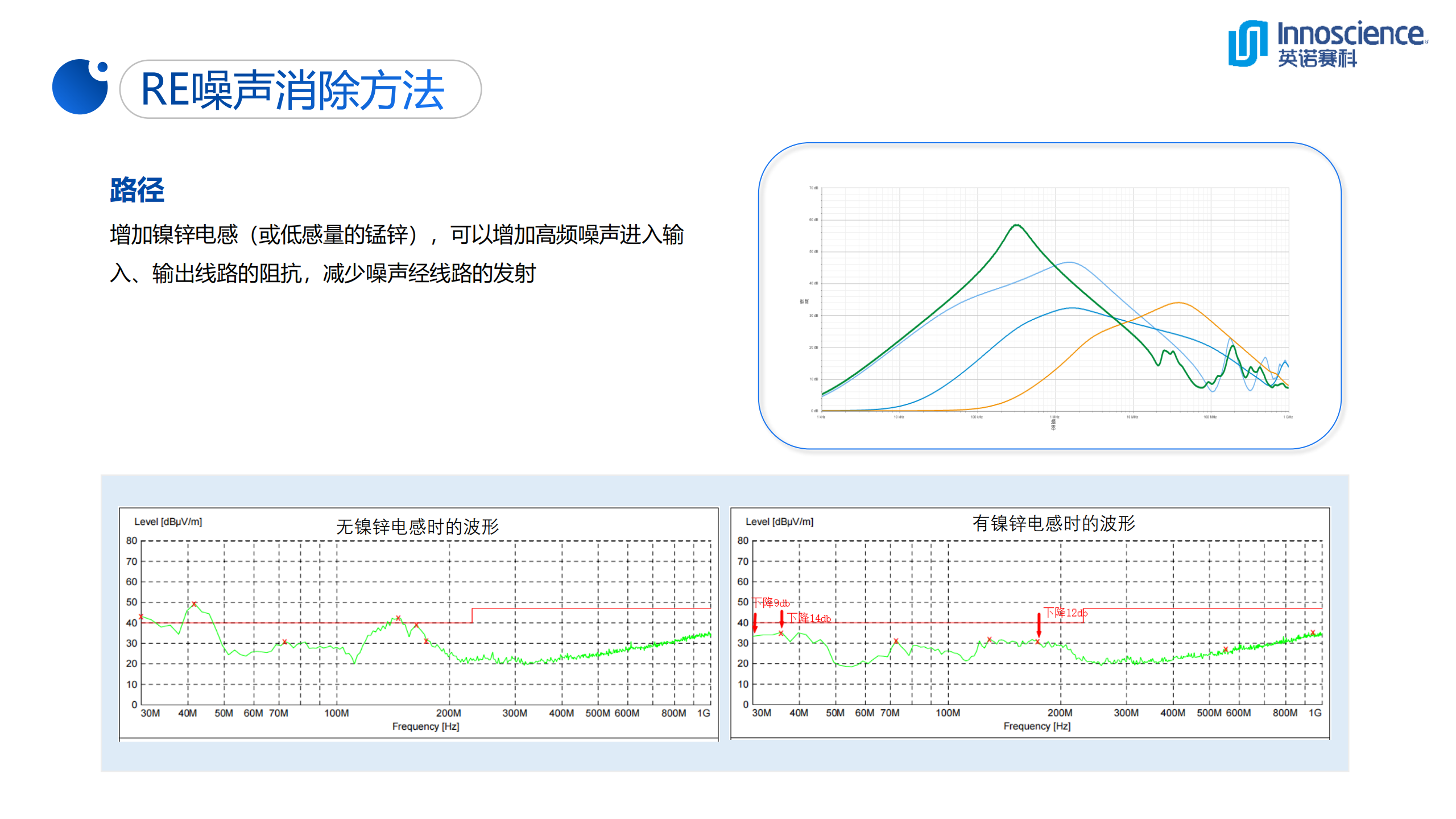

输入、输出的镍锌电感或低感量锰锌电感,可以减少进入输入、输出线路上的RE噪声。根据噪声峰值频率的不同,选择合适的磁环,可以获得该峰值噪声的最佳衰减效果。

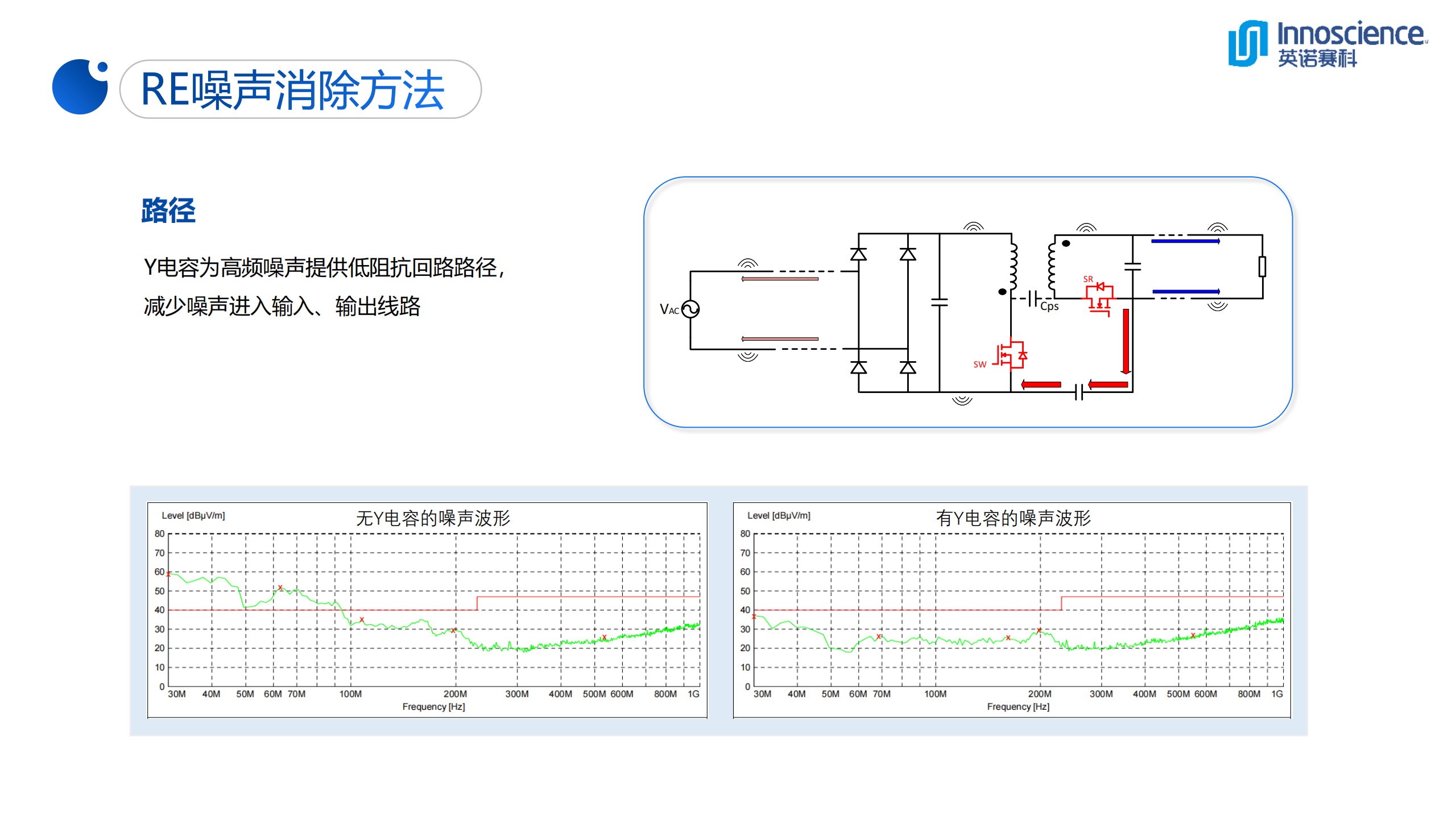

Y电容也是RE噪声的低阻抗回路,减小高频噪声对外发射。

以上介绍了高功率密度设计的关键点,1是物理上尺寸做小,2是效率做高,3就是解决EMC。我们来看以下基于INNOGAN的33W单C和A+C的解决方案。

单C解决方案的尺寸为26*26*26mm,功率密度为1.88W/CC,采用双板堆叠,加工简单,同时效率高,温度低。

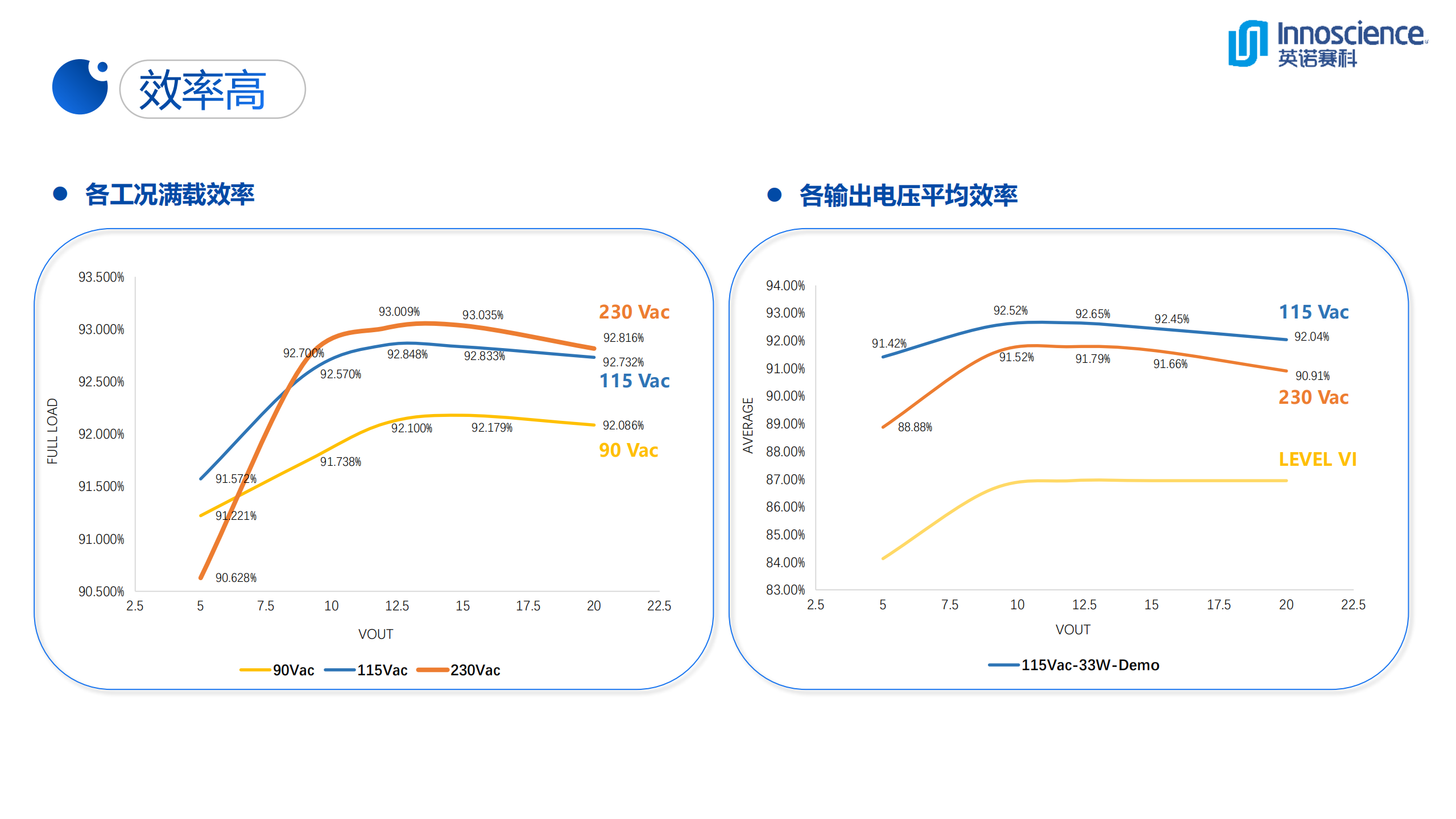

33W可以在全电压范围内做到高于92%的效率,同时平均效率远高于六级能效的要求。

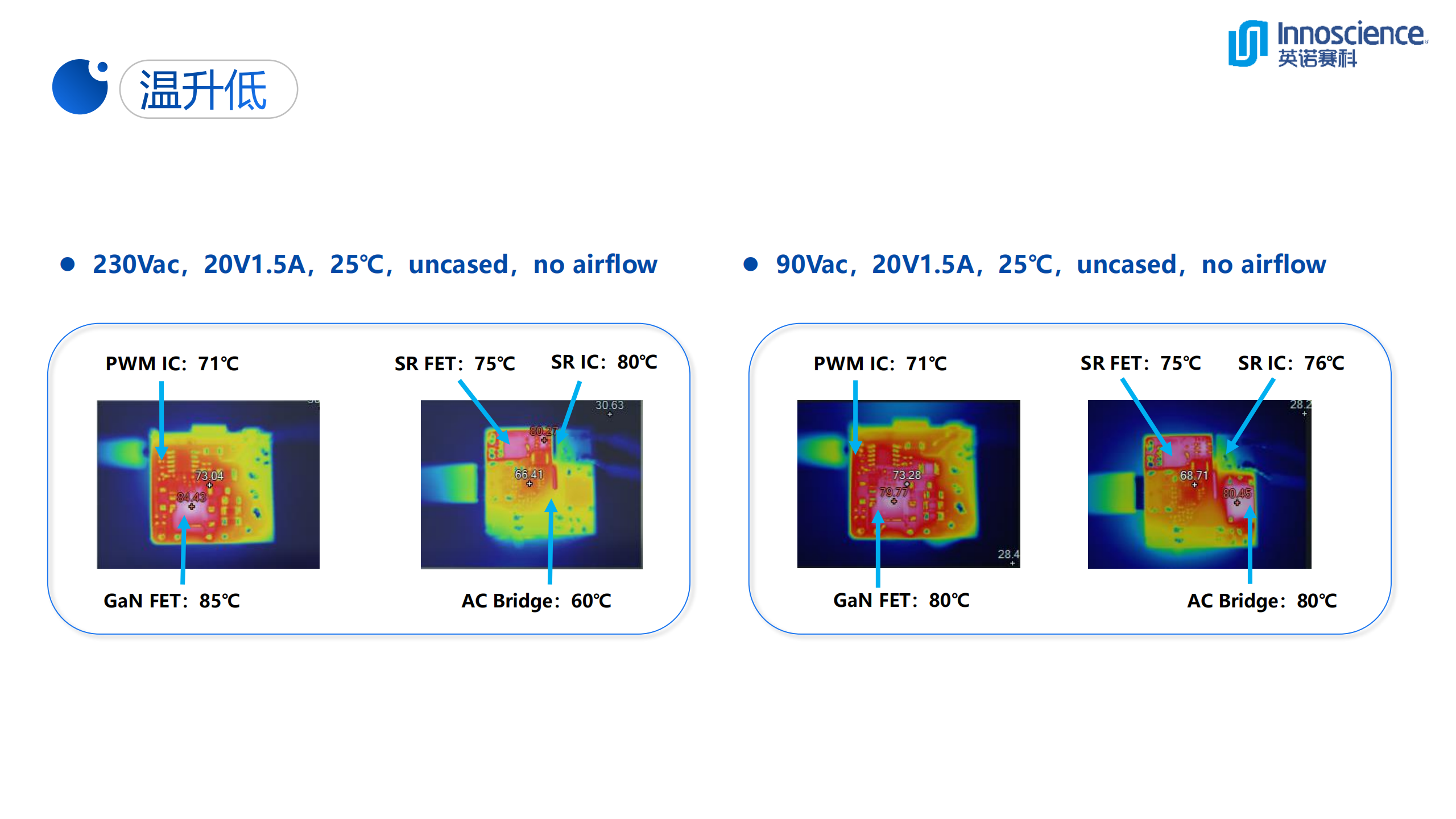

由于效率较高,器件的温度在高低压都能在80℃左右。

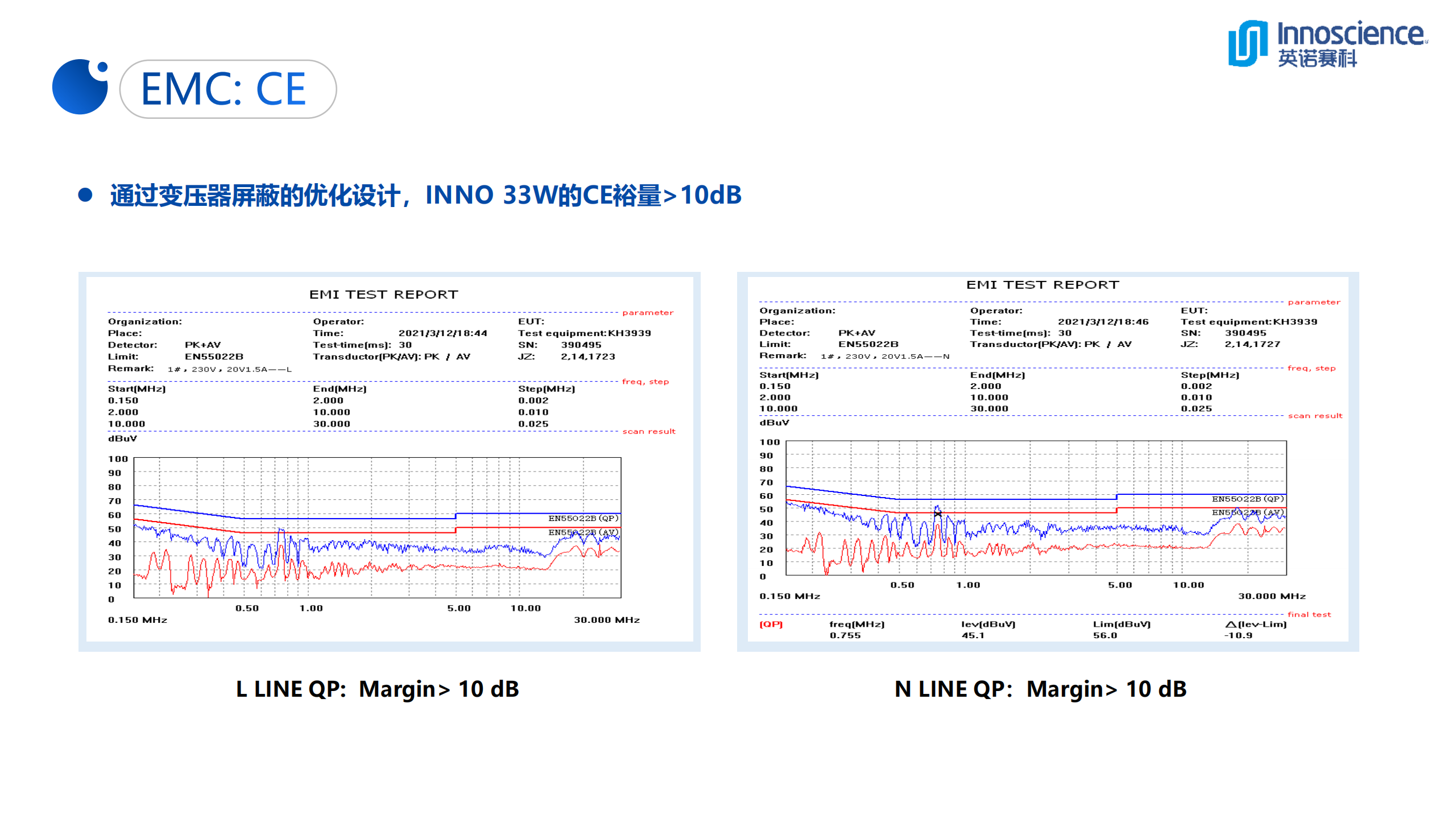

CE这块通过变压器屏蔽抵消的优化设计,可以实现10dB以上的裕量。

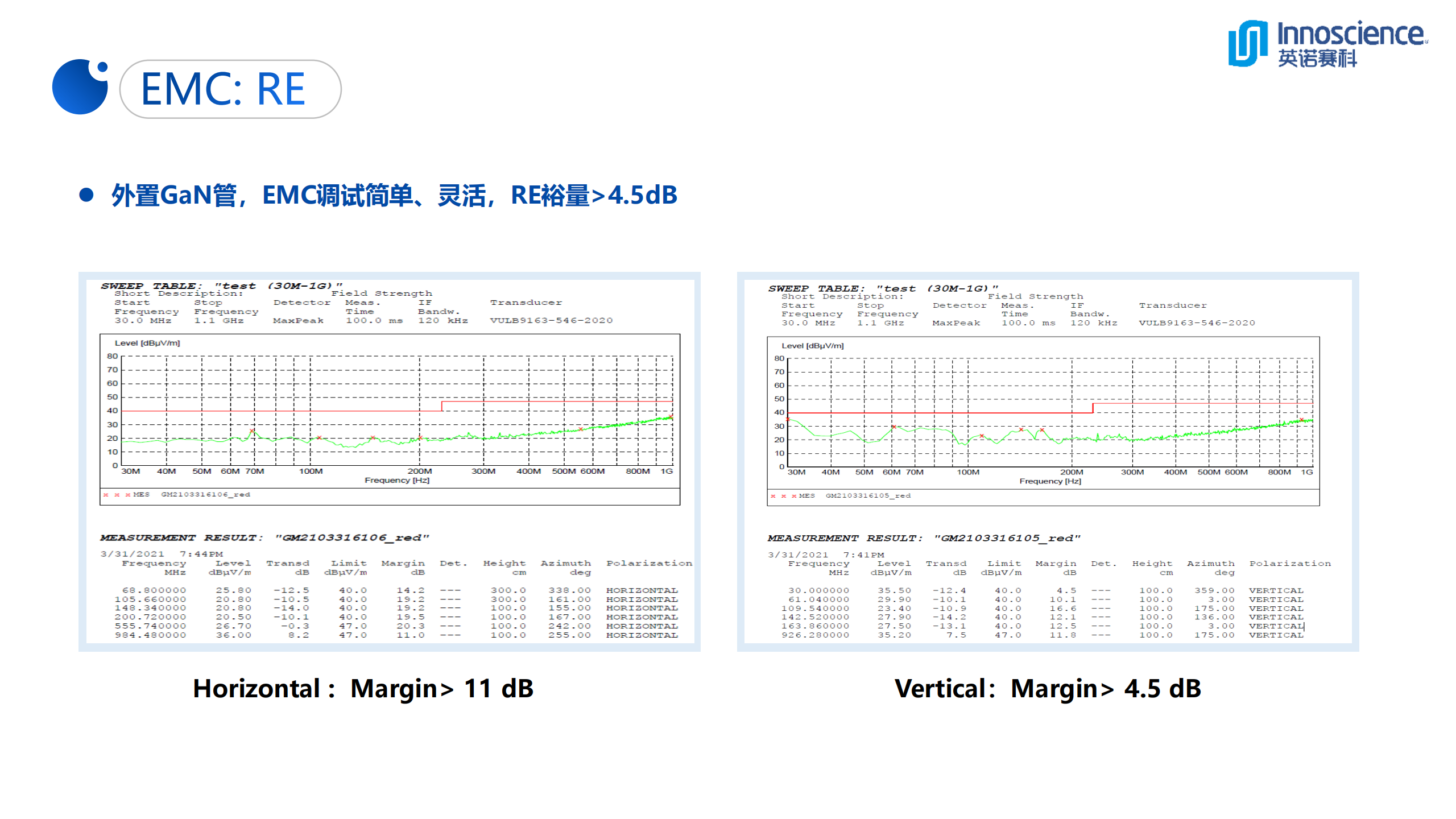

RE方面通过封装优势和灵活调整驱动参数,可以做到4dB以上的裕量。

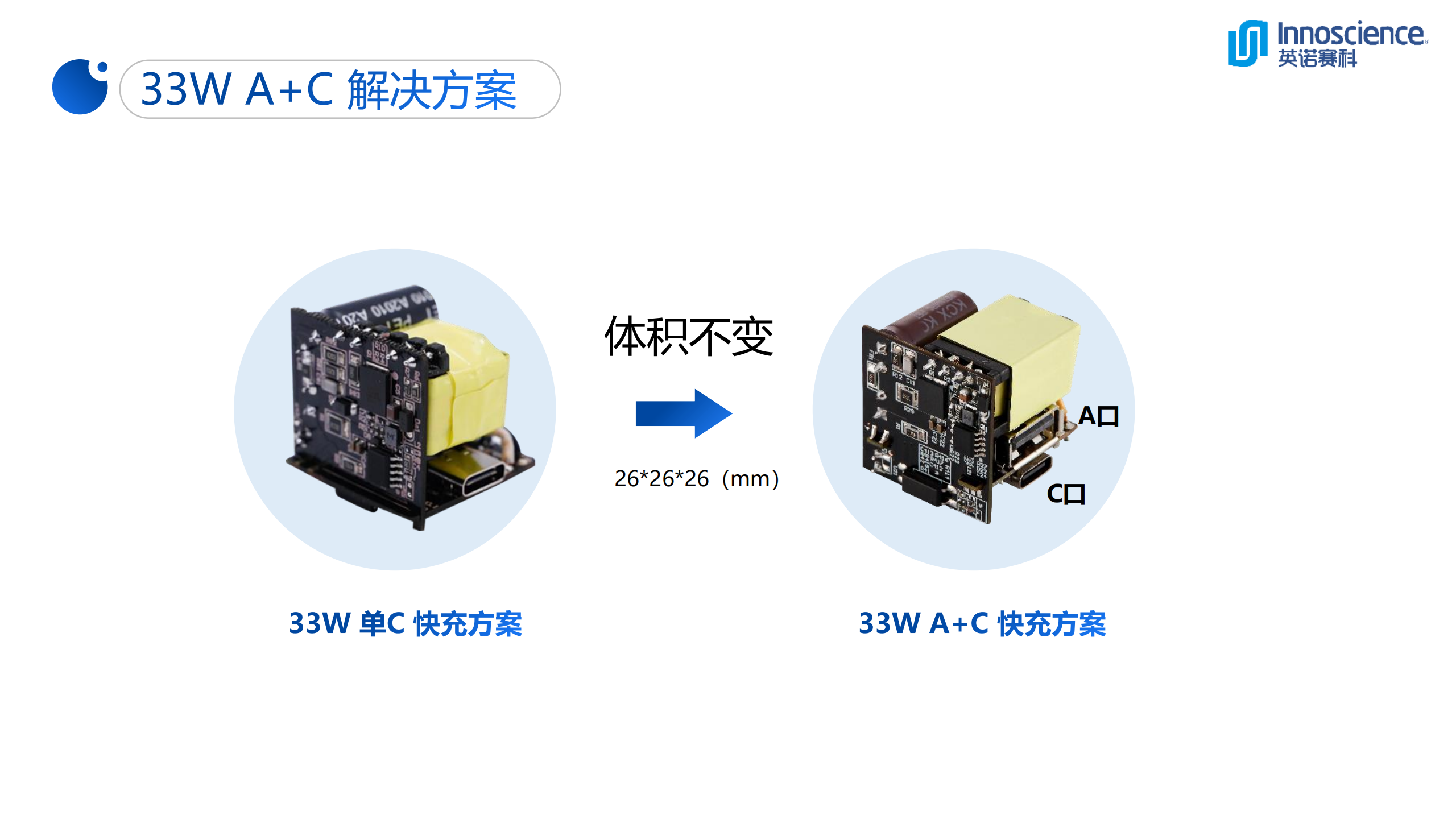

最后是33W A+C方案,考虑到客户有A+C的需求,英诺赛科基于单C方案优化空间布局,在体积不变的情况下,设计出来33W A+C的方案。

英诺赛科推出的33W氮化镓快充,通过氮化镓器件强大的性能优势与全方位的优化。成功实现了小体积高效率的33W氮化镓方案,并且实现33W的A+C输出,提高适配器的通用性,相比单口竞争力更强。

评论 (0)